#### THESIS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

# On control of cascaded H-bridge converters for STATCOM applications

EHSAN BEHROUZIAN

Department of Electrical Engineering Division of Electric Power Engineering CHALMERS UNIVERSITY OF TECHNOLOGY Gothenburg, Sweden, 2017 On control of cascaded H-bridge converters for STATCOM applications EHSAN BEHROUZIAN ISBN 978-91-7597-638-9

© EHSAN BEHROUZIAN, 2017.

Doktorsavhandlingar vid Chalmers Tekniska Högskola Ny serie nr. 4319 ISSN 0346-718X

Department of Electrical Engineering Division of Electric Power Engineering Chalmers University of Technology SE–412 96 Gothenburg Sweden Telephone +46 (0)31–772 1000

Printed by Chalmers Reproservice Gothenburg, Sweden, 2017

On control of cascaded H-bridge converters for STATCOM applications EHSAN BEHROUZIAN Department of Electrical Engineering Chalmers University of Technology

### **Abstract**

Cascaded H-bridge (CHB) converters are today considered the industrial standard for STAT-COM applications, mainly due to their small footprint, high achievable voltage levels, modularity and reduced losses. However, there are still areas of research that need to be investigated in order to improve the performance and the operational range of this converter topology for grid-applications. The aim of this thesis is to explore control and modulation schemes for the CHB-STATCOM, highlighting the advantages but also the challenges and possible pitfalls that this kind of topology presents for this specific application.

The first part of the thesis is dedicated to the two main modulation techniques for the CHB-STATCOM: the Phase-Shifted Pulse Width Modulation (PS-PWM) and the Level-Shifted PWM (LS-PWM) with cells sorting. In particular, the focus is on the impact of the adopted modulation technique on the active power distribution on the individual cells of the converter. When using PS-PWM, it is shown that non-ideal cancellation of the switching harmonics leads to a non-uniform active power distribution among the cells and thereby to the need for an additional control loop for individual DC-link voltage balancing. Theoretical analysis proves that a proper selection of the frequency modulation ratio leads to a more even power distribution over time, which in turns alleviates the role of the individual balancing control. Both PS-PWM and cells sorting schemes fail in cell voltage balancing when the converter is not exchanging reactive power with the grid (converter in zero-current mode). To overcome this problem, two methods for individual DC-link voltage balancing at zero-current mode are proposed and verified.

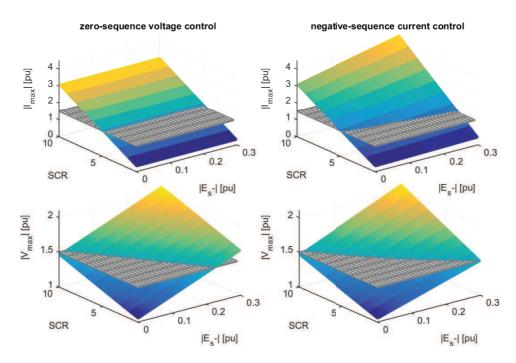

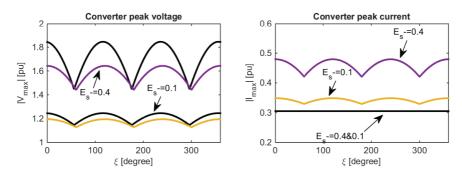

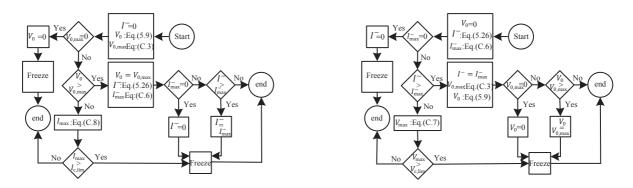

Then, the thesis focuses on the operation of the CHB-STATCOM under unbalanced conditions. Two different strategies for DC-link capacitor voltage balancing, based on zero-sequence voltage/current and negative-sequence current control, are investigated and compared. The comparison shows that none of the investigated control strategies allow for the full utilization of the converter capacity. Aiming at enhancing the converter utilization, two alternative control strategies, based on the proper combination of the zero-sequence and negative-sequence current control, are proposed and investigated.

Finally, the operation of the CHB-STATCOM when controlling the voltage at the connection point in case of unbalanced system conditions is considered. It is shown that even if the device is intended for compensation of the positive-sequence voltage only, control of the negative-sequence voltage might be necessary in order to avoid undesired overvoltages. Three structures for the negative-sequence voltage control are investigated and compared.

**Index Terms:** Modular Multilevel Converters (MMC), cascaded H-bridge converters, STATCOM, FACTS.

## Acknowledgments

First and foremost, I owe my deepest gratitude to my supervisor, Professor Massimo Bongiorno, you have been a tremendous mentor for me. I am extremely thankful for providing me an opportunity to do the PhD project work at Chalmers and giving me such a nice support and guidance through the rough road of finishing this thesis. Your academical and educational advices have been priceless. I would also like to thank my examiner Prof. Torbjörn Thiringer for his insightful comments.

I am also thankful to Dr. Stefan Lundberg for being my co-supervisor and for all the fruitful discussions for the laboratory set up. Moreover, I would like to thank Dr. Hector Zelaya De La Parra who was my co-supervisor in the beginning of this project. Unfortunately, Hector is not between us anymore but his memory with those unique and kind smiles will remain with us forever. Many thanks also go to Prof. Remus Teodorescu from Aalborg University for help with the laboratory set-up and for many nice discussions.

The financial support provided by ABB is gratefully acknowledged. I would like to thank Dr. Georgios Demetriades and Dr. Jan Svensson from ABB corporate research for several common meetings and for their insightful comments and encouragements throughout the course of this thesis. I would like to also thank Dr. Jean-Philippe Hasler from ABB power technologies FACTS and Dr. Christopher David Townsend (formerly with ABB corporate research) for their comments and feedback. My sincere thanks also goes to Dr. Konstantinos Papastergiou (formerly with ABB corporate research) who provided me an opportunity to come to Sweden and join his team as an intern before starting my PhD study.

Many thanks go to all members of the department for all the fun we have had in the past five years, in particular my office-mate Selam Chernet for making the office an enjoyable place to work.

A special thanks to my parents. Words cannot express how grateful I am to you for all of the sacrifices that you have made on my behalf. Finally, and most importantly, I would like to thank my beloved wife Mahtab. Thank you for your support, encouragement and patience during the hard period of writing this thesis. Also, I thank Mahtab's parents. Your help was invaluable when we were going through the most difficult situation.

Ehsan Behrouzian Gothenburg, Sweden October, 2017

# **List of Acronyms**

HVDC High Voltage DC

FACTS Flexible AC Transmission System

DG Distributed Generation

SVC Static Var Compensator

VSC Voltage Source Converter

STATCOM STATic synchronous COMpensator

NPC Neutral Point Clamped

ANPC Active Neutral Point Clamped CCC Capacitor Clamp Converter MMC Modular Multilevel Converter

CHB Cascaded H-Bridge

PWM Pulse Width Modulation

PS-PWM Phase shifted PWM

THD Total Harmonic Distortion

LS-PWM Level Shifted PWM PD-PWM Phase Disposition PWM

POD-PWM Phase Opposition Disposition PWM

APOD-PWM Alternate Phase Opposition Disposition PWM

SVM Space Vector Modulation

SHE Selective Harmonic Elimination SHM Selective Harmonic Mitigation

NVC Nearest Vector Control NLC Nearest level Control

H-PWM Hybrid PWM

MPC Model Predictive Control SRF Synchronous Reference Frame

PR Proportional Resonant

TSO Transmission System Operators

DSP Digital Signal Processing

FPGA Field Programmable Gate Array

SCR Short Circuit Ratio

PLL Phase Locked Loop

LPF Low Pass Filter

MAF Moving Average Filter

DCM Distributed Commutations pulse-width Modulation

DSC Delayed Signal Cancellation DVCC Dual Vector Current Control

CC Current Controller

PCC Point of Common Coupling KVL Kirchhoff's Voltage Law

ZSVC Zero-Sequence Voltage Control

ZSCC Zero-Sequence Current Control

NSCC Negative-Sequence Current Control

# **Contents**

| Abstract |                                                                    |                                                |                                                                    |     |  |  |  |

|----------|--------------------------------------------------------------------|------------------------------------------------|--------------------------------------------------------------------|-----|--|--|--|

| A        | know                                                               | vledgments                                     |                                                                    | vii |  |  |  |

| Li       | st of A                                                            | Acrony                                         | cronyms                                                            |     |  |  |  |

| Co       | Contents                                                           |                                                |                                                                    |     |  |  |  |

| 1        | Introduction                                                       |                                                |                                                                    |     |  |  |  |

|          | 1.1                                                                | Backg                                          | round and motivation                                               | 1   |  |  |  |

|          | 1.2                                                                |                                                | se of the thesis and main contributions                            | 3   |  |  |  |

|          | 1.3                                                                |                                                | ure of the thesis                                                  | 4   |  |  |  |

|          | 1.4                                                                |                                                | f publications                                                     | 4   |  |  |  |

| 2        | Multilevel converter topologies and modulation techniques overview |                                                |                                                                    |     |  |  |  |

|          | 2.1                                                                | Introd                                         | uction                                                             | 7   |  |  |  |

|          | 2.2                                                                | Main                                           | multilevel converter topologies                                    | 8   |  |  |  |

|          |                                                                    | 2.2.1                                          | Neutral Point Clamped converter (NPC)                              | 8   |  |  |  |

|          |                                                                    | 2.2.2                                          | Capacitor Clamp Converter (CCC)                                    | 11  |  |  |  |

|          |                                                                    | 2.2.3                                          | Modular configurations                                             | 13  |  |  |  |

|          |                                                                    | 2.2.4                                          | Comparison of multilevel converter topologies for STATCOM applica- |     |  |  |  |

|          |                                                                    |                                                | tions                                                              | 15  |  |  |  |

|          | 2.3                                                                | Modular subset configurations and comparison   |                                                                    |     |  |  |  |

|          | 2.4                                                                | 2.4 Multilevel converter modulation techniques |                                                                    | 21  |  |  |  |

|          |                                                                    | 2.4.1                                          | Multicarrier PWM                                                   | 21  |  |  |  |

|          |                                                                    | 2.4.2                                          | Space Vector Modulation (SVM)                                      | 25  |  |  |  |

|          |                                                                    | 2.4.3                                          | Fundamental switching modulators                                   | 26  |  |  |  |

|          |                                                                    | 2.4.4                                          | Hybrid PWM (H-PWM)                                                 | 29  |  |  |  |

|          | 2.5                                                                | Concl                                          | usion                                                              | 29  |  |  |  |

| 3        | Overall control of CHB-STATCOM                                     |                                                |                                                                    |     |  |  |  |

|          | 3.1                                                                |                                                | uction                                                             | 31  |  |  |  |

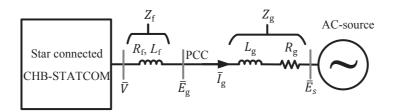

|          | 3.2                                                                | CHB-                                           | STATCOM modeling and control                                       | 32  |  |  |  |

|          |                                                                    | 3.2.1                                          | System modeling                                                    | 32  |  |  |  |

|          |                                                                    | 3 2 2                                          | Steady-state analysis                                              | 34  |  |  |  |

### Contents

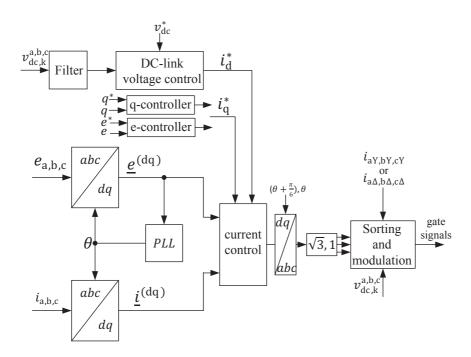

|   |     | 3.2.3    | Control design and algorithm                                        | . 35  |

|---|-----|----------|---------------------------------------------------------------------|-------|

|   |     | 3.2.4    | Phase-Locked Loop (PLL)                                             |       |

|   |     | 3.2.5    | DC-link filter design                                               |       |

|   | 3.3 | Digital  | control and main practical problems                                 |       |

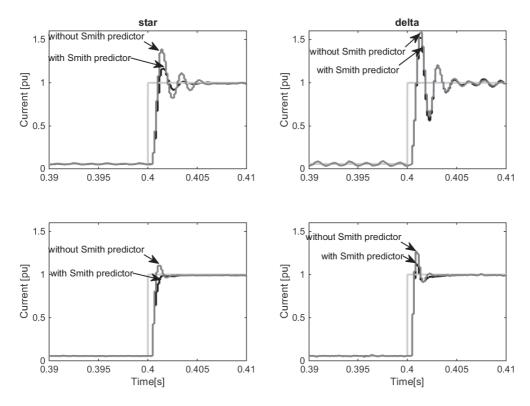

|   |     | 3.3.1    | One-sample delay compensation                                       |       |

|   |     | 3.3.2    | Saturation and Integrator Anti-windup                               |       |

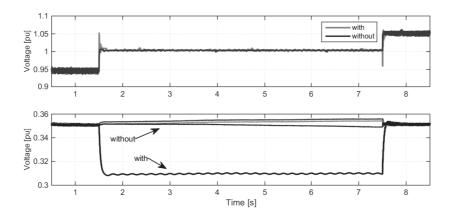

|   | 3.4 | Simula   | ation results                                                       |       |

|   | 3.5 | Conclu   |                                                                     |       |

| 4 | CHI | CTAT     | COM modulation and individual DC-link voltage balancing             | 51    |

| 4 | 4.1 |          | action                                                              |       |

|   | 4.1 |          | shifted PWM harmonic analysis                                       |       |

|   | 4.2 | 4.2.1    |                                                                     |       |

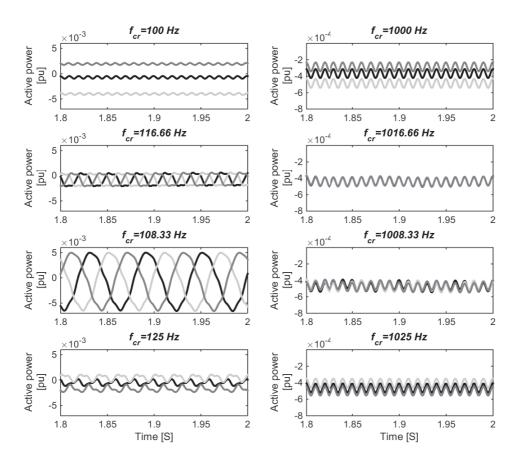

|   |     | 4.2.1    | Effect of side-band harmonics on the active power                   |       |

|   |     | 4.2.2    | ± •                                                                 | . 30  |

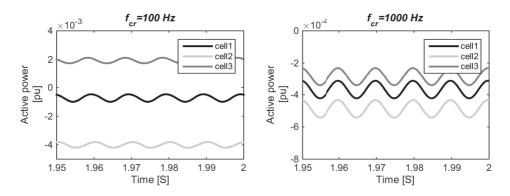

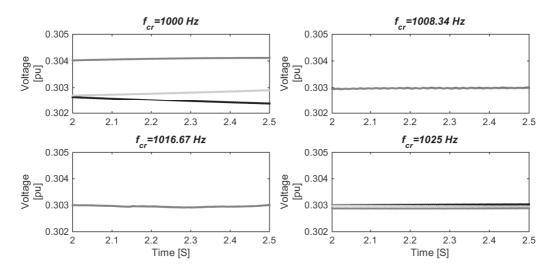

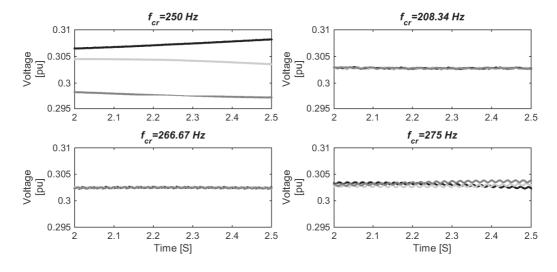

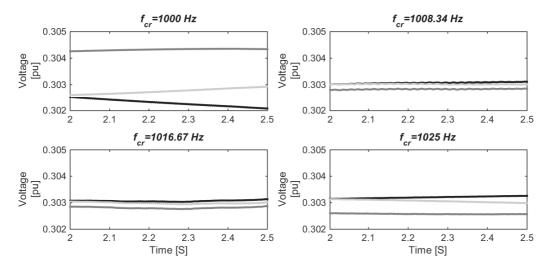

|   |     | 4.2.3    | Impact of non-integer frequency modulation ratio for high switching | . 59  |

|   |     | 4.2.4    | frequencies                                                         |       |

|   | 4.2 |          | Simulation results                                                  |       |

|   | 4.3 |          | lual DC-link voltage controller                                     |       |

|   | 4 4 | 4.3.1    | Simulation results                                                  |       |

|   | 4.4 |          | lual DC-link voltage control using sorting approach                 |       |

|   |     | 4.4.1    | Sorting approach and modulation technique                           |       |

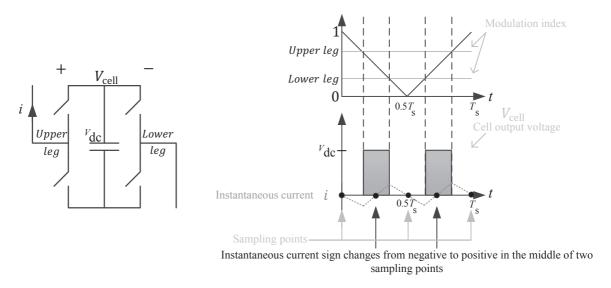

|   |     | 4.4.2    | Zero-current operating mode                                         |       |

|   |     | 4.4.3    | Modified sorting approach                                           |       |

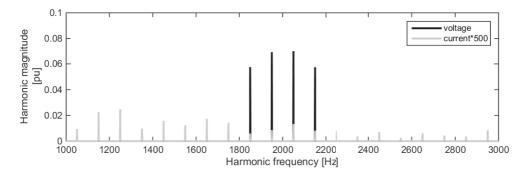

|   |     | 4.4.4    | DC-link voltage modulation                                          |       |

|   | 4.5 | 4.4.5    | Simulation results                                                  |       |

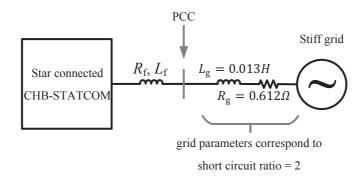

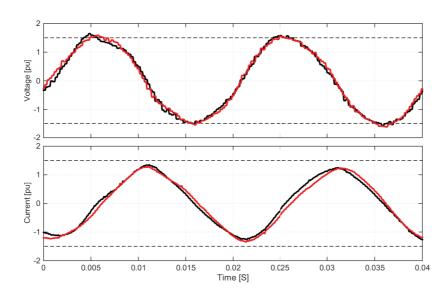

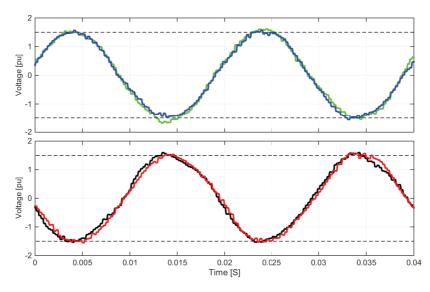

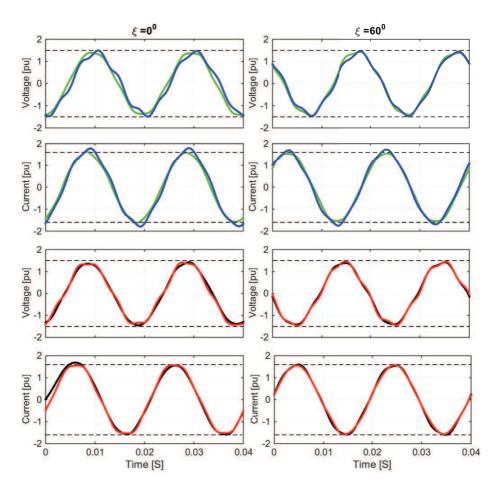

|   | 4.5 | -        | mental results                                                      |       |

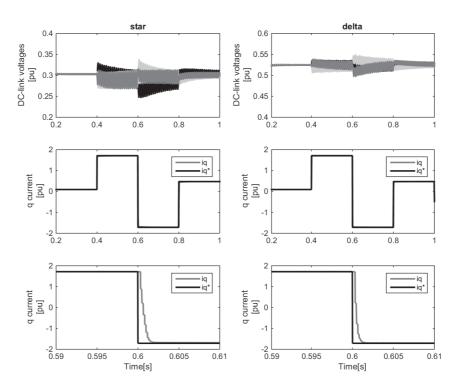

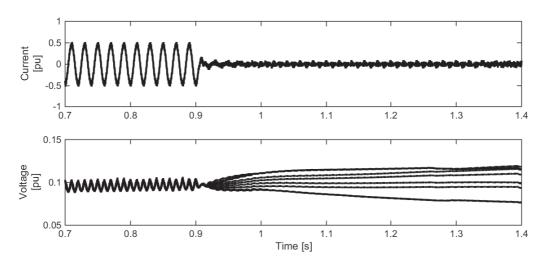

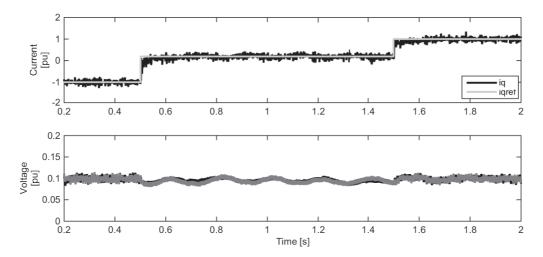

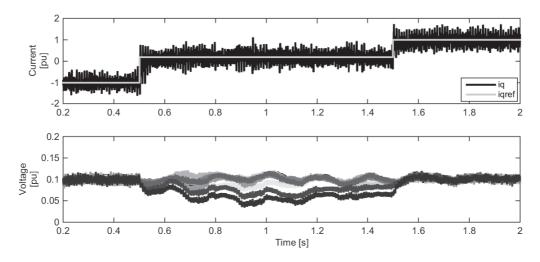

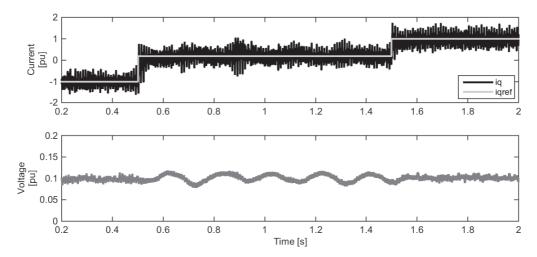

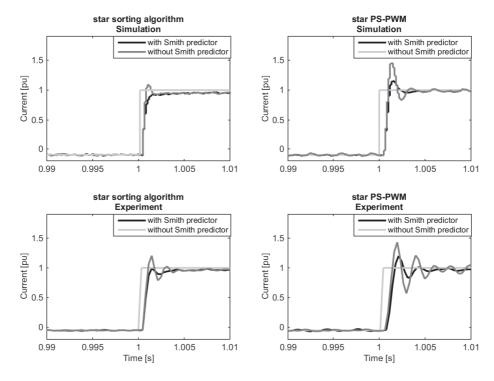

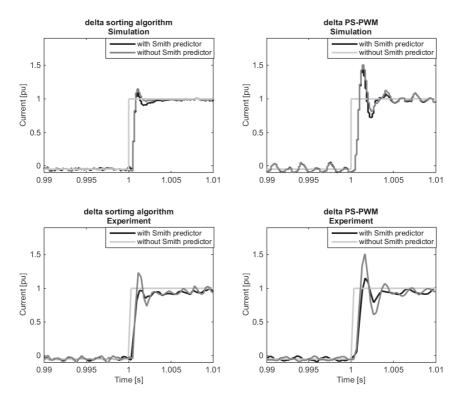

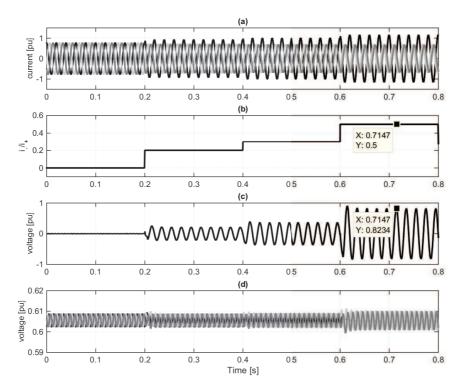

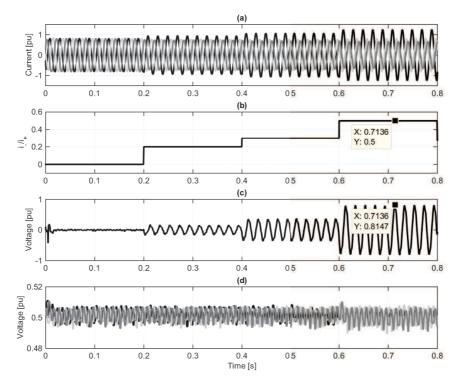

|   |     | 4.5.1    | Dynamic performances of CHB-STATCOMs                                |       |

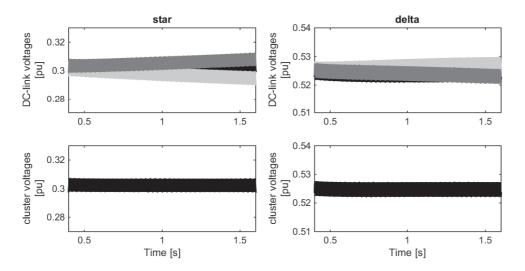

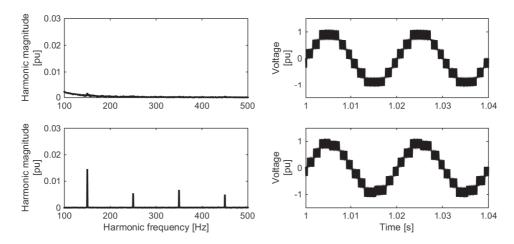

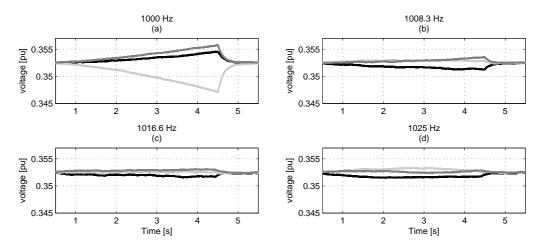

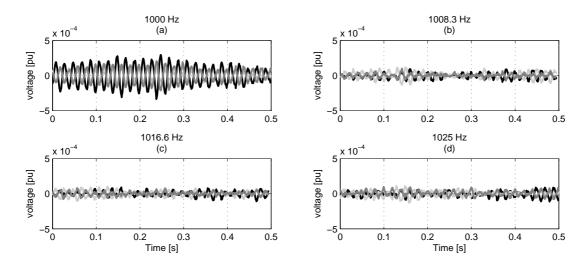

|   |     | 4.5.2    | Integer versus non-integer carrier frequency modulation ratio       |       |

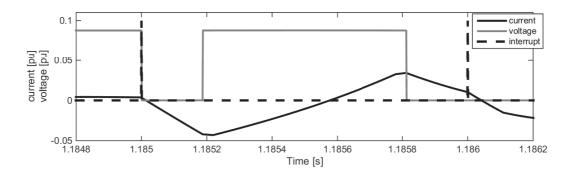

|   |     | 4.5.3    | DC-link voltage modulation technique and zero-current mode          |       |

|   | 4.6 | Conclu   | asion                                                               | . 99  |

| 5 | Ope | ration o | of CHB-STATCOM under unbalanced conditions                          | 101   |

|   | 5.1 | Introdu  | action                                                              | . 101 |

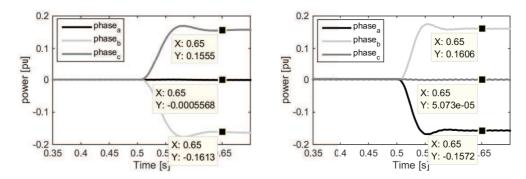

|   | 5.2 | Impact   | of unbalanced conditions on active power distribution               | . 102 |

|   | 5.3 | -        | equence control under unbalanced conditions                         |       |

|   | 5.4 |          | of CHB-STATCOM for unbalanced operations                            |       |

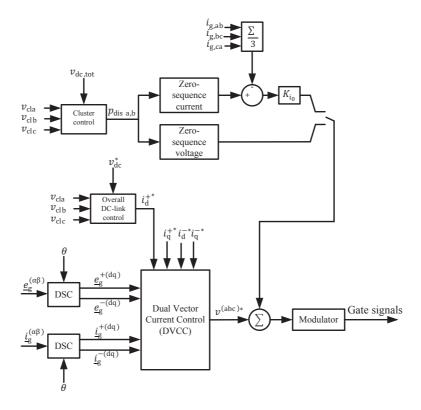

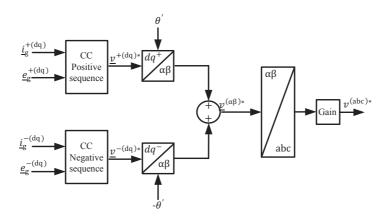

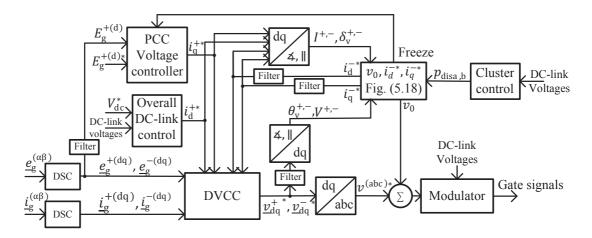

|   |     | 5.4.1    | Dual Vector Current-controller (DVCC)                               |       |

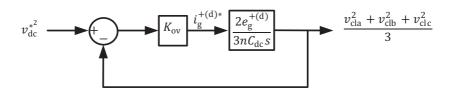

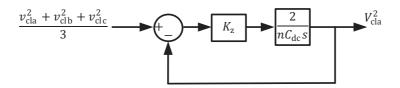

|   |     | 5.4.2    | Modified DC-link voltage control                                    |       |

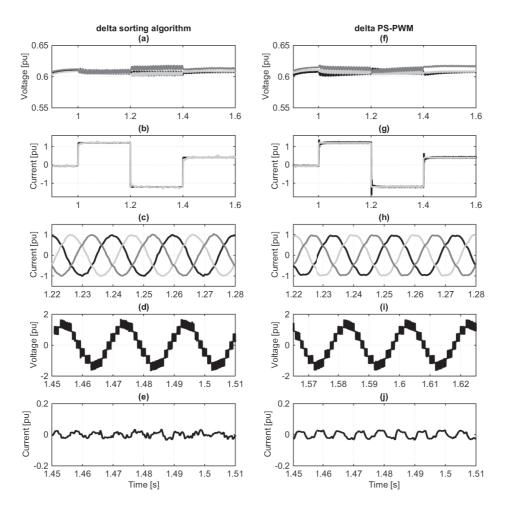

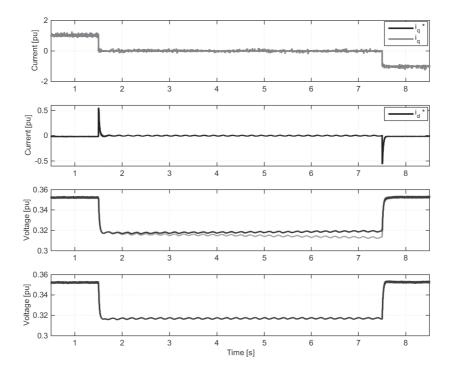

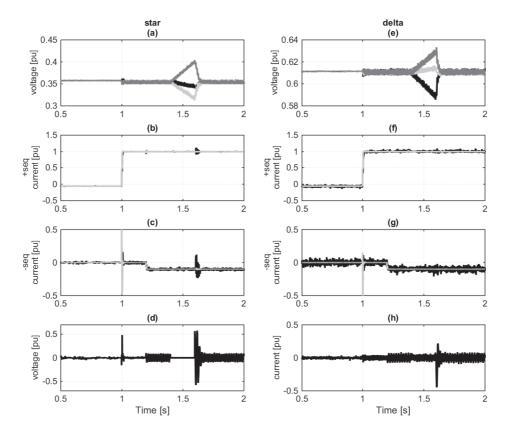

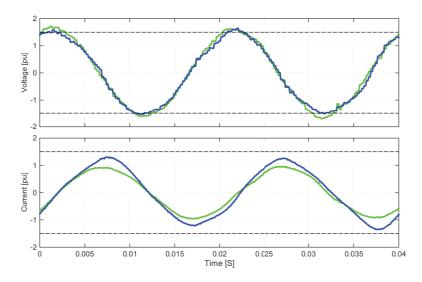

|   |     | 5.4.3    | Experimental results                                                |       |

|   | 5.5 |          | ing range of CHB-STATCOM when using zero-sequence control           |       |

|   |     | 5.5.1    | Theoretical analysis                                                |       |

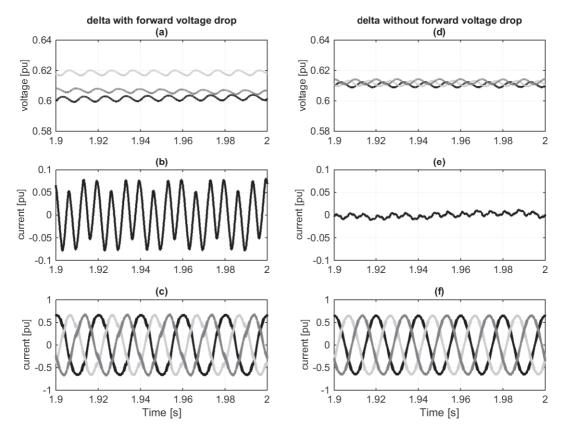

|   |     | 5.5.2    | Simulation and experimental results                                 |       |

|   |     | 5.5.3    | Discussion                                                          |       |

|   | 5.6 |          | ve-Sequence Current Control (NSCC) under unbalanced conditions      |       |

|    | 5.7                                                  | Comparison between the two balancing strategies                        |     |  |  |

|----|------------------------------------------------------|------------------------------------------------------------------------|-----|--|--|

|    |                                                      | 5.7.1 Steady-state analysis of ZSVC                                    |     |  |  |

|    |                                                      | 5.7.2 Steady-state analysis of NSCC                                    |     |  |  |

|    |                                                      | 5.7.3 Theoretical results and discussion                               |     |  |  |

|    | 5.8                                                  | Combined balancing strategy                                            |     |  |  |

|    |                                                      | 5.8.1 Control algorithm                                                |     |  |  |

|    |                                                      | 5.8.2 Control implementation                                           |     |  |  |

|    |                                                      | 5.8.3 Experimental results                                             |     |  |  |

|    | 5.9                                                  | Impact of PCC voltage regulation in case of unbalanced grid conditions |     |  |  |

|    |                                                      | 5.9.1 Negative-sequence voltage control                                |     |  |  |

|    | 5.10                                                 | Conclusions                                                            | 144 |  |  |

| 6  | Conclusions and future work                          |                                                                        |     |  |  |

|    | 6.1                                                  |                                                                        | 147 |  |  |

|    | 6.2                                                  | Future work                                                            | 149 |  |  |

| Re | eferen                                               | ces                                                                    | 151 |  |  |

| A  | Tran                                                 | sformations for three-phase systems                                    | 161 |  |  |

|    | A.1                                                  | Introduction                                                           | 161 |  |  |

|    | A.2                                                  | Transformations of three-phase quantities into vector                  | 161 |  |  |

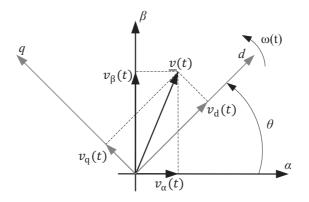

|    |                                                      | A.2.1 Transformations between fixed and rotating coordinate systems    | 162 |  |  |

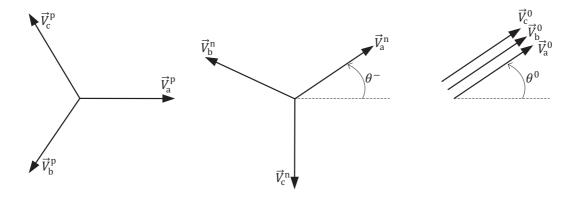

|    | A.3                                                  | Voltage vectors for unbalanced conditions                              | 163 |  |  |

| В  | Symmetrical component basics                         |                                                                        |     |  |  |

|    | B.1                                                  | Introduction                                                           | 165 |  |  |

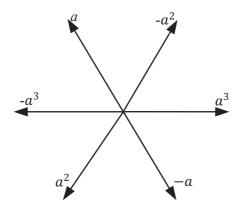

|    | B.2                                                  | Positive, negative and zero sequence extraction                        | 165 |  |  |

| C  | Calculation guideline for the combined ZSVC and NSCC |                                                                        |     |  |  |

|    | C.1                                                  | Introduction                                                           | 171 |  |  |

|    | C.2                                                  | Maximum allowable zero-sequence voltage                                | 171 |  |  |

|    | C.3                                                  | Maximum allowable negative-sequence current                            |     |  |  |

|    | C.4                                                  | Peak voltage calculation                                               |     |  |  |

|    | C 5                                                  | Peak current calculation                                               |     |  |  |

### Contents

# **Chapter 1**

# Introduction

# 1.1 Background and motivation

Interconnected transmission systems are complex and require careful planning, design and operation. The continuous growth of the electrical power system, as well as the increasing electric power demand, has put a lot of emphasis on system operation and control. These topics are becoming more and more of interest, in particular due to the recent trend towards restructuring and deregulating of the power supplies [1][2]. It is under this scenario that the use of High Voltage Direct Current (HVDC) and Flexible AC Transmission Systems (FACTS) controllers represents important opportunities and challenges for optimum utilization of existing facilities and to prevent outages [2][3].

Typically, FACTS devices are divided into two main categories: series-connected and shuntconnected configurations [2][3]. At the actual stage, shunt-connected FACTS devices are dominating the market for controllable devices, mainly due to the inherited reactive characteristic of series capacitors and to the complications in the protection system for series devices. Shuntconnected reactive power compensators are available both based on mature thyristor-based technology (named Static Var Compensator, SVC) and on Voltage Source Converter (VSC) technology, also known under the name of STATic COMpensator (STATCOM). The thyristorbased technology is today the preferred option for installations having high-power ratings (typically above several hundreds of MVar) [2]. On the other hand, the VSC technology is the most suitable choice when high speed of response or small footprint is needed. Furthermore, the use of VSC technology allows low harmonic pollution in the injected/absorbed current as compared with the SVC. These items, together with a higher operational flexibility and good dynamic characteristics under various operating conditions (for example, large variations in the short-circuit strength of the grid at the connecting point), indicate that the VSC technology is qualitatively superior relative to the thyristor-based SVC for static shunt compensation. Although today the STATCOM is more expensive than the SVC, its technical benefits together with the advancements in the technology are slowly leading to a shift from the thyristor-based to the VSC-based technology, similarly to the ongoing process in the HVDC area.

STATCOMs have been widely applied both in regional and distribution grids, mainly to miti-

#### Chapter 1. Introduction

gate power quality phenomena [4], and at transmission and sub-transmission level for voltage control, load shedding and power oscillations damping [2–4]. Furthermore, the STATCOM can be utilized in renewable-based power plants, mainly for grid-codes fulfillment and to allow fast reactive power compensation [5]. In case of renewable-based power plants, an interesting feature of the STATCOM is the possibility of incorporating an energy storage to the DC side of the VSC, thus allowing temporary active power exchange (for example, to limit power fluctuations).

The use of high-performance and cost-effective high power VSCs is a prerequisite for the realization of a STATCOM. Up to some years ago, the implementation of VSCs for high-power applications was difficult due to the limitations in the semiconductor devices. Typical voltage ratings for semiconductors are between 3 kV and 6 kV, which represent only a small fraction of the system rated voltage. For this reason, series-connection of static switches was needed in the VSC design for FACTS applications. Furthermore, the need to keep down the power losses has severely limited the level of the switching frequency that could be used in actual installations, leading to relatively large filtering stages. For these reasons, in the last decades multilevel converters for high-power application have gained more and more attention [6]. Among the multilevel VSCs family, the modular configurations such as Cascaded H-Bridge (CHB) converters are the most interesting solutions for high-power grid-connected converter [7].

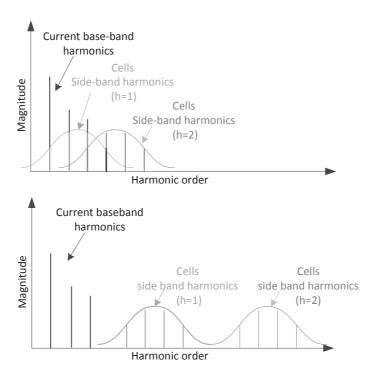

Although CHB converter are today the accepted solution for the implementation of FACTS devices, challenges still exist both from a control and from a design point of view. In the recent years, both manufacturers and researches have paid high effort to improve the control and the modulation of this converter topology. For the latter, Phase-Shifted Pulse Width Modulation (PS-PWM) [8] and the cells sorting approach [9, 10] has been extensively investigated in the literature. However, not sufficient attention has been given to the investigation of the different harmonic components that are generated when using PS-PWM and their impact on the system performance, in particular in case of non-ideal conditions of the system.

In [11], the use of a non-integer frequency modulation ratio (defined as the ratio between the frequency of the carrier and the grid frequency) is investigated. This work mainly focuses on the interaction between the cell voltage carrier harmonics and the fundamental component of the arm current. However, in case of CHB converters with reduced number of cells (such as for STATCOM applications), carrier harmonics in the current must also be taken into account. Furthermore, [11] does not provide any guideline for the reader on the selection of the frequency modulation ratio when trying to minimize the DC voltage divergence.

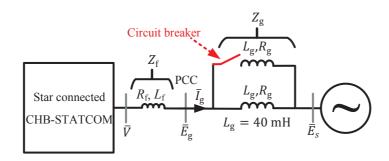

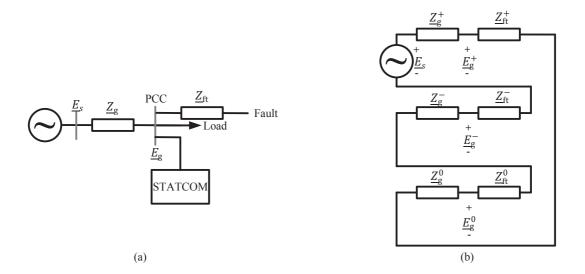

Another challenge regarding the CHB-STATCOMs is their control under unbalanced conditions. In particular, in case of star-connected CHB-STATCOM, when the system is exchanging negative-sequence current with the grid a zero-sequence voltage must be introduced in the output phase voltage of the converter to guarantee capacitor balancing [12–15]. On the other hand, the delta configuration allows negative-sequence compensation by letting a zero-sequence current circulate inside the delta [16–18].

In the work presented in [19][20], the star-connected CHB is considered as the most suitable configuration for positive-sequence reactive power control, typically for voltage regulation purpose and, more in general, for utility applications; on the other hand, delta configuration is considered to be the best solution for applications where negative-sequence is required, as it is

the case for industrial applications (for example, flicker mitigation).

However, requirements from Transmission System Operators (TSOs) are changing and start to demand negative-sequence injection capability for the converters connected to their grid [21]. Furthermore, the delta configuration can present limitations in injecting negative-sequence current in case of weak grids, where both load current and voltage are unbalanced, or under unbalanced fault conditions [20]. This kind of investigation is missing in today's literature. For this reason, it is of high importance to investigate the limits in terms of negative-sequence compensation for this kind of configurations.

# 1.2 Purpose of the thesis and main contributions

The aim of this thesis is to explore control and modulation schemes for the CHB-STATCOM, both under balanced and unbalanced conditions of the grid, highlighting the advantages but also the challenges and possible pitfalls that this kind of topology presents for this specific application.

Based on the described purpose, the following specific contributions can be identified:

- Control of CHB-STATCOMs at zero-current mode: It is shown that although existing approaches for individual DC-link voltage control are able to provide an appropriate voltage control, they are not able to provide a proper DC-link voltage control when the converter is operated at zero-current mode. Two methods for individual DC-link voltage balancing at zero-current mode are proposed and analyzed. The first method is based on a modified sorting approach and the second method is based on DC-link voltage modulation. Using the proposed methods, proper individual DC-link voltage balancing is achieved at zero-current mode.

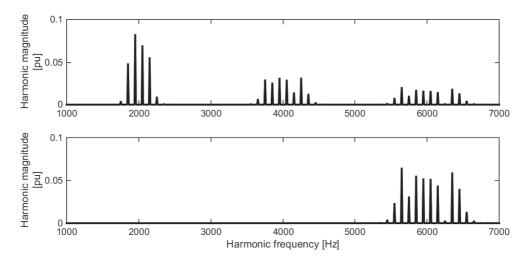

- Investigation of Phase-Shifted PWM: It is shown that poor cancellation of harmonics of Phase-Shifted PWM (PS-PWM) leads to non-uniform power distribution among cells. Theoretical analysis shows that by proper selection of the frequency modulation ratio, a more even power distribution among the different cells of the same phase leg can be achieved, which alleviates the roll of the individual DC-link voltage control.

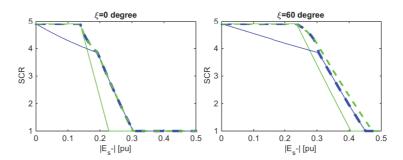

- DC-link voltage balancing using zero-sequence components: It is shown that a singularity in the solution of the zero-sequence component exists, which in turn limits the operational range of these converters under unbalanced conditions. The singularity in the delta configuration occurs when the positive- and negative-sequence components of the voltage at the converter terminals are equal, while for the star it is governed by the equality between the positive- and the negative-sequence component of the injected current. In addition to the amplitudes, the phase angles of currents in star and voltage in delta will highly impact the sensitivity of the converter. For the star configuration, the highest demand on the zero-sequence voltage occurs when the three-phase positive-sequence currents are aligned with the negative-sequence tern; on the contrary, the lowest demand

#### Chapter 1. Introduction

on the zero-sequence component occurs when the two terns are in phase opposition. Analogue results hold for the delta case.

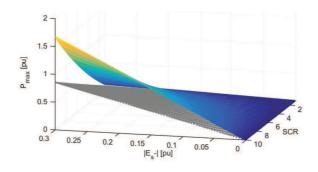

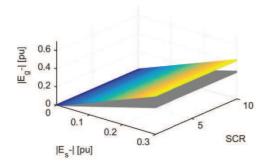

- Negative-sequence current and zero-sequence component comparison: negative-sequence current control is also a solution for DC-link voltage balancing. Negative-sequence current and zero-sequence component strategies are compared and their impact on the converter ratings under different unbalanced conditions is evaluated. The impact of the grid Short Circuit Ratio (SCR) is highlighted. It is shown that none of the investigated control strategies allow for a full utilization of the converter voltage, indicating that these strategies must combined in an appropriate way. Thus, a method to effectively combine the two strategies, based on zero-sequence voltage or negative-sequence current priority, is described and investigated.

- Negative-sequence voltage control: the operation of the CHB-STATCOM when controlling the voltage at the connection point in case of unbalanced voltage dips is investigated. It is shown that even if the device is intended for compensation of the positive-sequence voltage only, control of the negative-sequence voltage might be necessary in order to avoid overvoltages in the unfaulted phases. Three types of negative-sequence voltage control are investigated and compared.

The theoretical outcomes and control algorithms are verified both analytically and through dynamic simulations. The obtained theoretical results are also verified experimentally.

### 1.3 Structure of the thesis

The thesis is organized into six chapters with the first chapter describing the background information, motivation and contribution of the thesis. Since the focus of the thesis is on multilevel converters, Chapter 2 gives an overview of the main multilevel converter topologies and their modulation techniques. Chapter 3 provides the basic control structure for star and delta configurations, under balanced conditions. Chapter 4 investigates the harmonic performance of the CHB-STATCOM when PS-PWM is used in the modulation stage and also focuses on the individual DC-link voltage balancing. Chapter 5 deals with unbalanced conditions. Two DC-link voltage balancing strategies are presented and compared together with two alternative combined strategies to extend the converter's utilization. In the same chapter, three different negative-sequence voltage controllers are investigated and compared. Finally, the thesis concludes with the summary of the achieved results and suggestions for future work in Chapter 6.

# 1.4 List of publications

This Ph.D. project has resulted in the following publications, which constitute the majority of the thesis.

- I. E. Behrouzian, M. Bongiorno and H. Zelaya De La Parra, "An overview of multilevel converter topologies for grid connected applications," in *Proc. of Power Electronics and Applications (EPE 2013-ECCE Europe)*, in proceedings of the 2013-15th European Conference on, pp. 1-10, 2-6 Sept. 2013.

- II. E. Behrouzian, M. Bongiorno and H. Zelaya De La Parra, "Investigation of negative sequence injection capability in H-bridge multilevel STATCOM," in *Proc. of Power Electronics and Applications (EPE 2014-ECCE Europe), in proceedings of the 2014-16th European Conference on*, pp. 1-10, 26-28 Aug. 2014.

- III. E. Behrouzian, M. Bongiorno and R. Teodorescu, "Impact of frequency modulation ratio on capacitor cells balancing in phase-shifted PWM based chain-link STATCOM," in *Proc. of Energy Conversion Congress and Exposition (ECCE)*, 2014 IEEE, pp. 1931-1938, 14-18 Sept. 2014.

- IV. E. Behrouzian, M. Bongiorno, R. Teodorescu and J.P. Hasler, "Individual capacitor voltage balancing in H-bridge cascaded multilevel STATCOM at zero current operating mode," in *Proc. of Power Electronics and Applications (EPE 2015-ECCE Europe), in proceedings of the 2015-17th European Conference on*, pp. 1-10, 8-10 Sept. 2015.

- V. E. Behrouzian, M. Bongiorno and R. Teodorescu, "Impact of switching harmonics on capacitor cells balancing in phase-shifted PWM based cascaded H-Bridge STATCOM," *IEEE Trans. on Power Electro.*, vol.32, no.1, pp. 815-824, Jan. 2017.

- VI. E. Behrouzian and M. Bongiorno, "Investigation of negative-sequence injection capability of cascaded H-Bridge converters in Star and Delta configuration," *IEEE Trans. on Power Electro.*, vol.32, no.2, pp. 1675-1683, Feb. 2017.

- VII. E. Behrouzian and M. Bongiorno, "Impact of capacitor balancing strategies on converter ratings for star-connected cascaded H-bridge STATCOM," in *Proc. of Power Electronics and Applications (EPE 2017-ECCE Europe), in proceedings of the 2017-19th European Conference on*, pp. 1-10, 12-14 Sept. 2017.

- VIII. E. Behrouzian and M. Bongiorno, "DC-link voltage modulation for individual capacitor voltage balancing in cascaded H-Bridge STATCOM at zero current mode," submitted to *IET Power Electronics*.

- IX. E. Behrouzian and M. Bongiorno, "Impact of dc-link voltage balancing strategies on operational range of cascaded H-bridge converters for STATCOM application," submitted to *IEEE Trans. on Power Electro.*.

The author has also contributed to the following publications.

I. E. Behrouzian, A. Tabesh, F. Bahrainian and A. Zamani, "Power electronics for photo-voltaic energy system of an Oceanographic buoy," in *Proc. of Applied Power Electronics Colloquium (IAPEC-2011)*, pp. 1-4, 18-19 April 2011.

### Chapter 1. Introduction

- II. E. Behrouzin, A. Tabesh, A. Zamani, "A reliable and efficient circuitry for photovoltaic energy harvesting for powering marine instrumentations," in *Proc. of Renewable Power Generation (RPG-2011), IET Conference on*, pp. 1-4, 6-8 Sept. 2011.

- III. E. Behrouzian, K.D. Papastergiou, "A hybrid photovoltaic and battery energy storage system for high power grid-connected applications," in *Proc. of Power Electronics and Applications (EPE-2013), in proceedings of the 2013-15th European Conference on*, pp. 1-10, 2-6 Sept. 2013.

# Chapter 2

# Multilevel converter topologies and modulation techniques overview

### 2.1 Introduction

The concept of multilevel converters was first introduced in 1975 [22]. Multilevel converters are power conversion systems composed by an array of power semiconductors and several DC voltage sources. In the last decades, several multilevel converter topologies have been developed [23–27]. The elementary concept of a multilevel converter is to build up a high output voltage through several lower DC voltage sources. The voltage rating of each power semiconductor is kept at only a fraction of the output voltage. The output voltage waveform of a multilevel converter is then synthesized by selecting different voltage levels obtained from the DC voltage sources.

Depending on the selected topology, the number of levels of a multilevel converter can be defined as the number of constant voltage values that can be generated between the output terminal and a reference node within the converter. Generally, different voltage steps are equidistant from each other. Each phase of the converter has to generate at least three voltage levels in order to be included in the multilevel converter family.

A multilevel converter presents several advantages and disadvantages over a traditional two-level converter. Some of the advantages can be summarized as follows [23–27].

- A multilevel converter generates an output voltage with lower distortion and reduced  $\frac{dv}{dt}$ .

- For the same harmonic spectrum of the converter output voltage, the switching frequency

of the power semiconductors can be much lower. This leads to lower switching losses and

thereby higher efficiency.

- Since the voltage rating of each power semiconductor can be kept at only a fraction of the output voltage, the stress across power semiconductors reduces and consequently lower ratings for power semiconductors are required.

### Chapter 2. Multilevel converter topologies and modulation techniques overview

• It facilitates transformer-less installations for grid connected applications.

On the other hand, some of the disadvantages are [23–27]:

- A multilevel converter comprises a greater number of power semiconductors. This leads to a more complex system, which negatively impacts the system reliability. Control and modulation of such a converter is also more challenging as compared with the two-level solution.

- For some topologies there is a practical limit in the achievable number of levels. The complexity in the control is one the most important determining factors in the number of achievable levels.

Many papers discussed about multilevel converter topologies, comparison between them [28–30] and their modulation techniques [27] [31]. The aim of this chapter is to provide an overview of different multilevel converter topologies and modulation techniques, with focus on STAT-COM applications. Advantages and disadvantages of three basic multilevel converters, the Neutral Point Clamped Converter (NPC), Capacitor Clamp Converter (CCC) and modular configurations will be discussed. In particular, different topologies will be compared in terms of number of components, DC-link capacitor dimensioning, modularity and controllability.

# 2.2 Main multilevel converter topologies

## 2.2.1 Neutral Point Clamped converter (NPC)

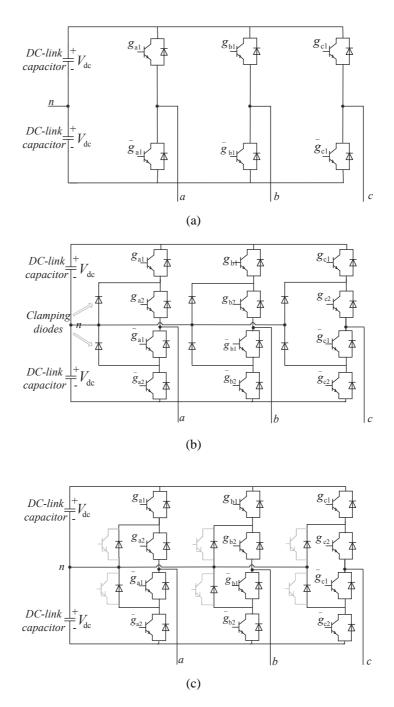

The NPC was first introduced by Nabae et al., in 1981 [32]. Figure 2.1(b) shows a three phase three-level NPC. This converter is based on the modification of the two-level converter (shown in Fig. 2.1(a)) adding two additional power semiconductors per phase. Using this configuration, each power semiconductor can be rated at half voltage as compared with a two-level converter having the same DC bus voltage. In another words, with the same power semiconductor rating as for the two-level converter, the voltage can be doubled in NPC. In addition, NPC allows to generate a zero-voltage level, obtaining a total of three different voltage levels. Figure 2.1(c) [33] shows another configuration of NPC called Active Neutral Point Clamped (ANPC), which will be discussed later.

Fig. 2.1 (a) Classic two-level converter, (b) Three-phase three-level NPC, (c) ANPC.

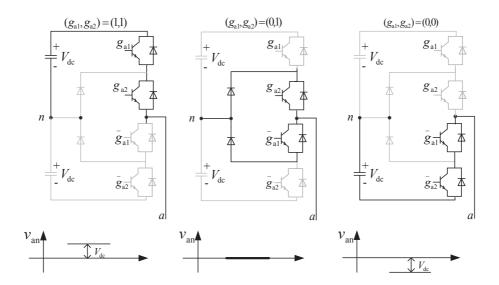

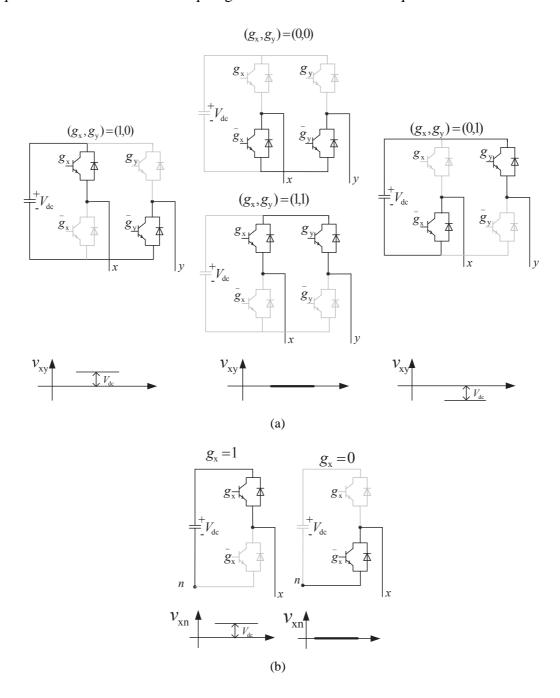

Figure 2.2 shows the different switching states for one phase leg of the three-level NPC and their corresponding output voltage levels. Current path for each set of gate control signals are highlighted. Note that there are only two control gate signals per phase. The other two gate signals are inverted to avoid to short circuit the DC-link. In Fig. 2.2, ON state of each power semiconductor is represented by 1 and OFF state is represented by 0. Gate signals  $(g_{a1}, g_{a2}) = (1,0)$  is not used since this switching state does not provide any current path at the output. The

Chapter 2. Multilevel converter topologies and modulation techniques overview

Fig. 2.2 Three-level NPC switching states and corresponding output voltage levels.

same switching states are also valid for the other two phases.

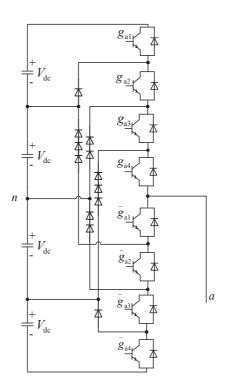

The NPC can be extended to higher number of output levels. For example Fig. 2.3 shows the phase leg of a five-level NPC. Although each power semiconductor device is rated at the voltage level of  $V_{\rm dc}$ , the clamping diodes require different ratings for reverse voltage blocking. For this reason, series connection of diodes, each rated for a voltage level of  $V_{\rm dc}$  are needed as in Fig. 2.3

NPC takes its name from the use of diodes to limit the collector-emitter voltages of the switching device to the voltage across one capacitor. Although it is theoretically possible to increase the number of levels, NPC finds its realistic limit to five-level due to the complexity of the system, complexity of the control and large number of components required [24]. Another limiting factor for the number of levels in NPC is represented by the uneven distribution of semiconductor losses among the semiconductors, which limits the switching frequency and the output power. The latter can be overcome by installing additional power semiconductors in parallel with the clamping diodes forming the so-called Active Neutral Point Clamped (ANPC) showed in Fig. 2.1(c) [33]. It is important to stress that although the power loss is more even in an ANPC, the need for more power electronic components leads to an increase in complexity of the overall system. In addition, the diode reverse recovery becomes an important design challenge. It is also of importance to mention that NPC does not present a modular configuration. Therefore series connection of power semiconductor is needed to achieve the desired voltage level for grid-connected applications. Thanks to the common DC link for all phases, the requirements on the DC-link capacitor are only to provide the temporary energy storage during switching operations, to distribute reactive power among the phases and to support the system losses. Despite the mentioned limitations, the NPC has been successfully implemented in STATCOM applications in its three-level topology with power level up to  $\pm 120$  MVA [34].

Fig. 2.3 Phase a of a five-level NPC.

### 2.2.2 Capacitor Clamp Converter (CCC)

The CCC was first introduced by Meynard et al., in 1992 [35]. Figure 2.4(a) shows a three phase three-level CCC. CCC can be considered as an alternative to overcome some of the NPC drawbacks. The main difference between this topology and the NPC is that the clamping diodes are replaced by clamping capacitors.

Figure 2.4(b) shows the different switching states for one phase leg of the three-level CCC and their corresponding output voltage levels. Current path for each set of gate control signals are highlighted. Similar to the NPC, only two control gate signals per phase leg are needed in order to avoid to short circuit the DC-link. However, in the CCC the inverted gating signals are related to different power semiconductors as compared with NPC, see Fig. 2.4(b). The output voltage levels of the converter are generated by adding or subtracting the clamping capacitor voltage to the DC bus voltage; for example, zero-voltage level in this topology is obtained by connecting the output of the converter to the neutral point (n in Fig. 2.4(b)) through clamping capacitor with opposite polarity with respect to the DC bus voltage. It should be noted that all four combinations of ( $g_{a1}, g_{a2}$ ) can be used in the CCC. Only three are shown in Fig. 2.4(b); both gate signals of ( $g_{a1}, g_{a2}$ ) can be used in the CCC. Only three zero-voltage level at the output.

Being able to generate the same voltage level with different switching states is known as voltage level redundancy. This redundancy plays an important role in the capacitor voltage balancing in a CCC. For example, in a five-level CCC there are six combinations of capacitor selection and switching states that generate zero-voltage level. By proper selection of the switching states and

### Chapter 2. Multilevel converter topologies and modulation techniques overview

capacitor combinations, it is possible to control the capacitor charging state. This can reduce the complexity of the capacitor voltage controller for higher levels [23]. The presence of a common DC link for the three phases is also an advantage of this topology.

Fig. 2.4 (a) Three-phase three-level CCC, (b) Three-level CCC switching states and their corresponding output voltage level, (c) Phase *a* of a four-level CCC.

The CCC can be extended to higher number of output levels. This can be observed by redrawing the CCC as illustrated in Fig. 2.4(c) for phase *a* of a four-level CCC. In Fig. 2.4(c), cell is refer to a pair of power semiconductor devices together with one capacitor. These cells (or modules) can be connected in cascaded form and each one provides one additional voltage level to the output. This property of the CCC has led to the idea that the CCC can be seen as a modular topology. However, the capacitors within each cell are charged to different voltage levels and this is in contrast with the modularity concept.

High number of voltage levels requires a relatively high number of capacitors in this topology. A m-level CCC requires a total of (m-1)(m-2)/2 clamping capacitors per phase in addition to the m-1 main DC-link capacitors. Lack of modularity and the high number of capacitors for high number of voltage levels can reduce the reliability of this converter. The size of the capacitors can also become large when using low switching frequency (typically, for switching frequencies below 800-1000 Hz), due to the fact that the output current flows through the clamping capacitor as long as the switching state does not change. However, being able to overcome the complexity in the control and hardware, a five-level CCC is implemented in STATCOM applications with voltage level up to 6.6kV [36].

### 2.2.3 Modular configurations

Modularity, in industrial design, refers to an engineering technique that builds large systems by combining smaller and identical subsystems. Designing power converter using the modularity concept was first introduced by Marchesoni et al., in 1990 [37]. A typical modular configuration consists of many identical cells connected in series. These cells can be either half- or full-bridge (H-bridge) converters. Figure 2.5 shows the half- and full-bridge cells together with their switching states and corresponding output voltage levels.

Different modular configurations will be shown in Section 2.3 but for illustration purpose, a single-line diagram of a five-level star configuration is shown in Fig. 2.6. This topology is capable of reaching high output voltage levels using only standard low-voltage technology components. Due to the modularity, in case of a fault in one cell, it is possible to replace it quickly and easily. Moreover, it is possible to bypass the faulty module without stopping the load, bringing an almost continuous overall availability.

Although modular configurations presents a fairly simple structure, they suffer from requirement of large number of cells (more isolated capacitors) to decrease the harmonics and the switching frequency. This leads to a more complex DC-voltage regulation loop. However various control algorithms exist to control high number of capacitors voltage [8]. Moreover, due to the lack of a common DC link, the output power will be affected by an oscillatory component having characteristic frequency equal to twice the grid frequency; these oscillations will be reflected on the DC-link voltage and therefore each cell necessitates over-sizing of the DC link capacitors to provide filtering effect.

Chapter 2. Multilevel converter topologies and modulation techniques overview

Fig. 2.5 Cell with switching states and corresponding output voltage level; (a): H-bridge; (b): half-bridge.

It is also possible to use cells with unequal DC-source voltages in modular configurations and form an alternative configuration called hybrid or asymmetric configuration [38]. The hybrid configuration can produce higher voltage level with fewer power electronic requirements. This reduces the size and cost as compared to the traditional modular configuration with equal DC links, since fewer semiconductors and capacitors are employed. The main disadvantage of this

Fig. 2.6 Single-line diagram of a five-level star configuration.

approach is that the converter is no longer modular in the strict interpretation of the term.

# 2.2.4 Comparison of multilevel converter topologies for STATCOM applications

In recent years, the demand for high-voltage conversion applications has drastically increased. Reliability, availability, controllability, modularity, number of components and losses are the main features for high power STATCOM applications.

In STATCOM applications, the converter voltage is increased through a step-up transformer before connecting to the grid. Consequently, the current will be high in the low voltage side, which leads to higher power loss and thus reduced efficiency. This is the driving force that has led the research community to focus on transform-less solutions, in order to directly connect the converter to the grid. In addition, a transformer-less topology allows a reduced footprint for the system and a reduction in losses. Since in high-voltage applications the voltage rating usually ranges several tens to hundreds of kVs, the power processing cannot be accomplished with any single IGBT or similar switch. One way to reach high voltage rating is to connect several switches in series and operate them simultaneously. However, the series operation of switches is very difficult because of tolerances in their characteristics and/or the unavoidable mismatch between the driving circuits. The main problem is to ensure an equal voltage sharing among the components during static and dynamic transient states. Furthermore, special arrangements are needed to guarantee a continuous operation of the device in case of a faulty switch.

A simpler method to increase the voltage rating is to use modular configurations. In these configurations the total output voltage of the converter can be increased by increasing the number of cells, each operated at low voltage. As mentioned before, it is possible to raise the voltage in modular configurations only by increasing the number of voltage levels. The ability of these configurations to increase the number of levels also results in better harmonic performance and

Chapter 2. Multilevel converter topologies and modulation techniques overview

TABLE 2.1. SUMMERY OF MULTILEVEL CONVERTERS CHARACTERISTICS

| structure                 | NPC        | CCC              | СНВ              |

|---------------------------|------------|------------------|------------------|

| Switches per phase        | 2(m-1)     | 2(m-1)           | 2(m-1)           |

| (Converter with m- level) |            |                  |                  |

| Clamping diodes per phase | (m-1)(m-2) | 0                | 0                |

| (Converter with m-level)  |            |                  |                  |

| Capacitors per phase      | (m-1)      | (m-1)(m-2)/2     | (m-1)/2          |

| (Converter with m-level)  |            | +(m-1)           |                  |

| Loss distribution         | Uniform    | Uniform          | Uniform          |

|                           | with ANPC  |                  |                  |

| Maximum practical levels  | 3-5 levels | 5-7 levels       | No theoretical   |

|                           |            |                  | limit            |

| Availability              | Low        | Low              | High             |

| Modularity                | No         | No               | Yes              |

| Capacitor sizing          | low        | high             | high             |

| Common DC source          | Yes        | Yes              | No               |

| Low switching             | Capable    | Capable with     | Capable with     |

|                           |            | large capacitors | large capacitors |

lower switching losses. These configurations also have the ability to successfully balance the capacitor voltages for high number of levels. It is for these reasons that the modular configurations are often considered as the most suitable solution to implement high-power STATCOM, while NPC and CCC are more suitable for medium-voltage and low-power applications. Table 2.1 summarizes different characteristics of multilevel converter topologies discussed in this section.

The main modular configurations are the star, delta and double star. In this thesis, the modular multilevel converters that are based on the use of H-bridge converters will be denoted as Cascaded H-Bridge (CHB) converters, while the converter based on half-bridge cells will be simply denoted as Modular Multilevel Converters (MMCs). Therefore, the star and delta configurations will be CHB converters, while the double start can be either CHB or MMC depending of the adopted cell topology. Each of these configurations has specific characteristics, advantages and disadvantages. A detailed review of these configurations is provided in the next section.

# 2.3 Modular subset configurations and comparison

The main modular configurations: star, delta and double star configurations [19] are investigated in this section and their application for STATCOM is addressed.

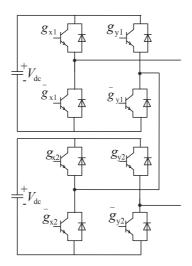

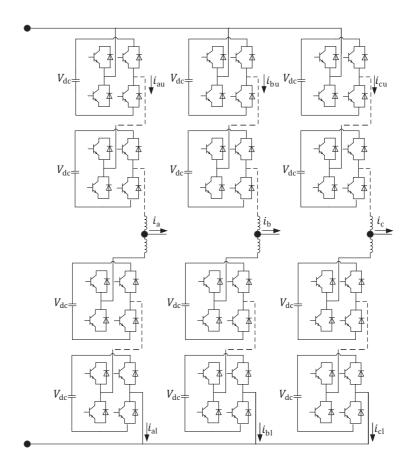

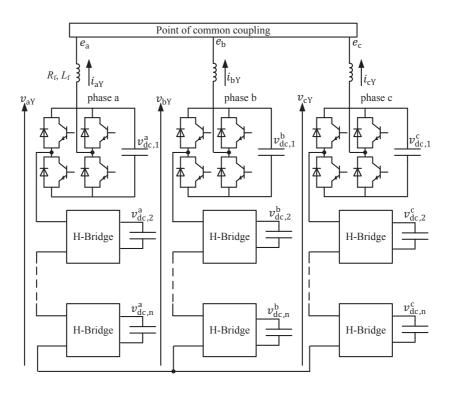

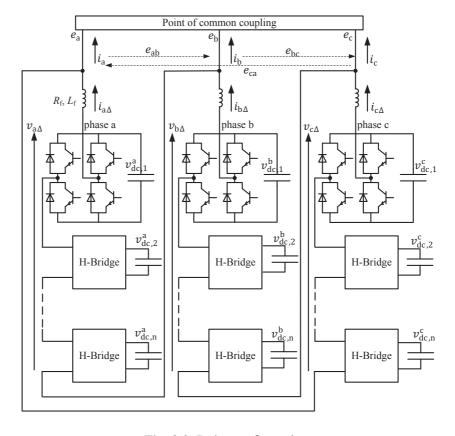

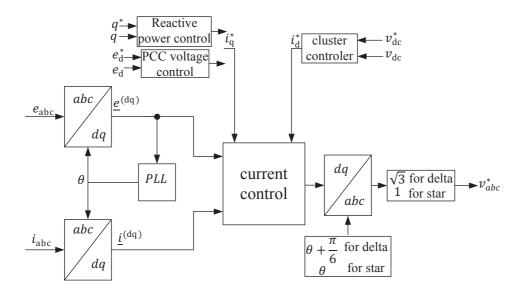

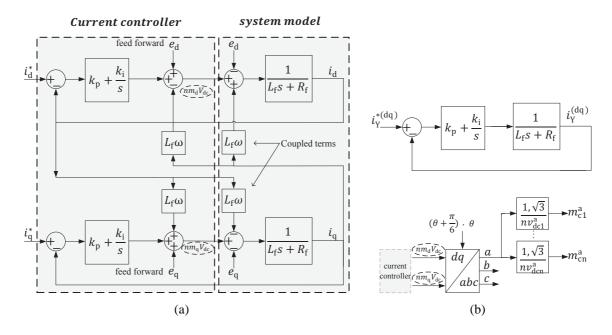

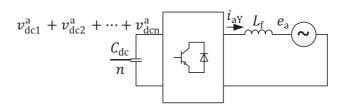

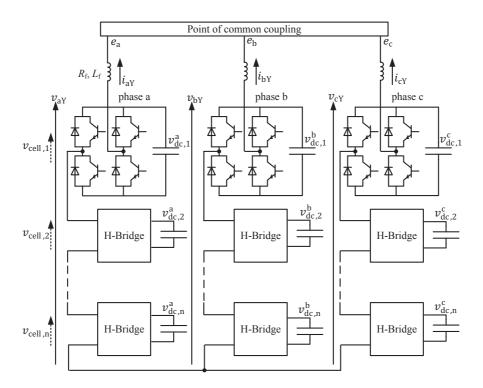

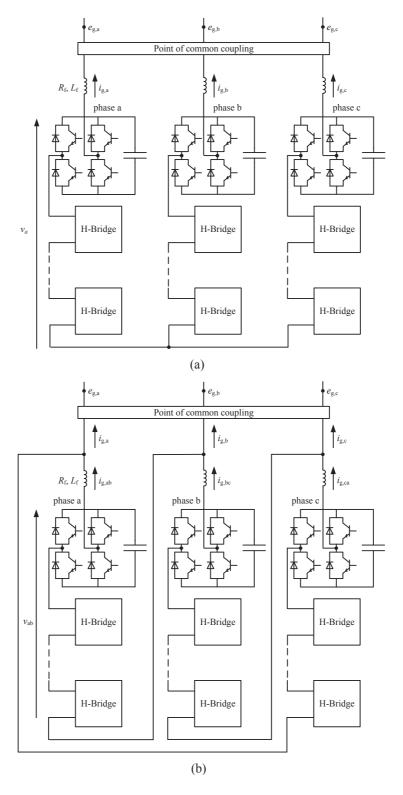

Star and delta configurations are shown in Fig. 2.7. Each phase consists of several H-bridge converters connected in series. Three phases can be connected in either star (*Y*, Fig. 2.7(a)) or delta (Δ, Fig. 2.7(b)). A prototype of star and delta configurations as three-phase STATCOM was first demonstrated by Peng et al., in 1996 [39]. In less than two years, in 1998, GEC ALSTHOM T&D (later ALSTOM T&D) proposed to use these configurations as a main power converter

Fig. 2.7 CHB configurations; (a): star configuration; (b): delta configuration.

in their STATCOMs. Robicon Corporation also commercialized their medium voltage drives utilizing these configurations in 1999. Currently these devices offer a power range of 10-250 MVAr [40, Chapter 2].

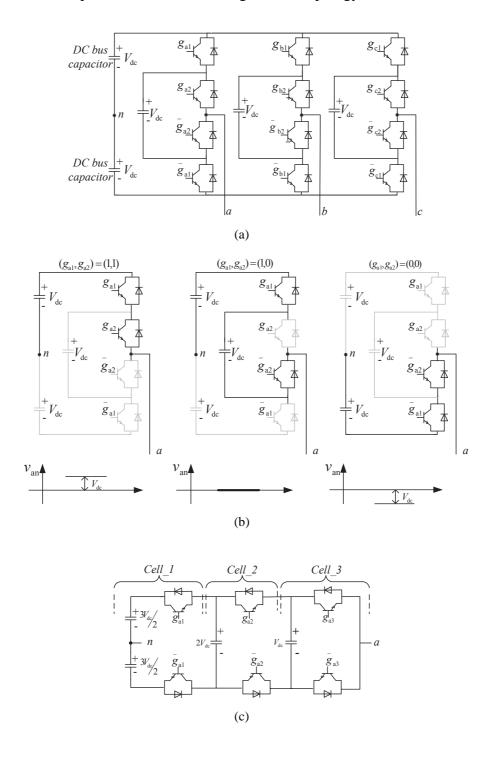

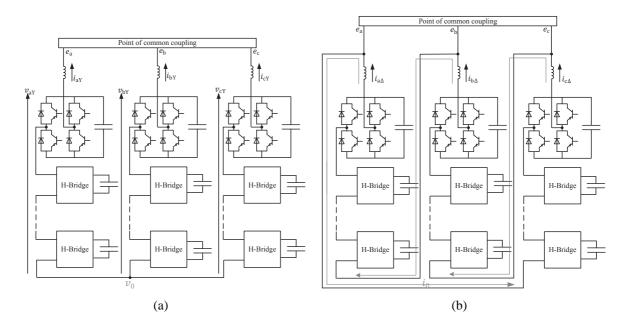

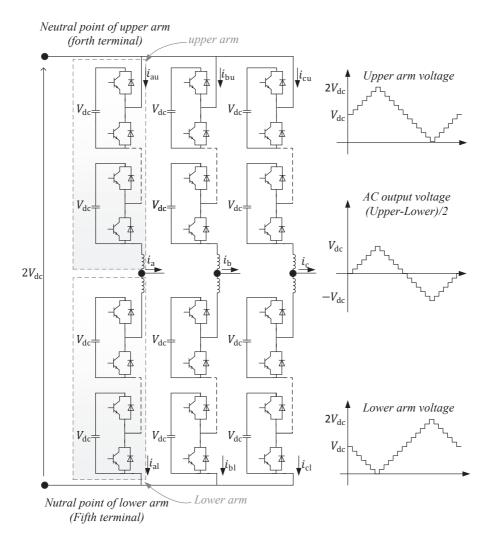

Another modular configuration that is receiving great research focus is the MMC, which was first introduced by Marquardt and Lesincar in 2003 [9]. This configuration is shown in Fig. 2.8. Each phase of the converter, also called converter leg, consists of two arms. Each arm contains equal number of cells together with a coupling inductor to limit the current under AC fault and also to limit the di/dt due to switching. The AC output is connected in the middle of the two arms. It is also possible to use H-bridge instead of half-bridge as illustrated in Fig. 2.9.

Comparing the star and delta configurations, the first difference is in their voltage and current rating. Under balanced grid voltage condition with equal number of cells per phase and similar power electronic equipment, star has  $\sqrt{3}$  time higher current rating compared to the delta, while delta has  $\sqrt{3}$  time higher voltage rating in each phase. In case of unbalanced grid voltage, delta has the ability to allow a controllable zero-sequence current that circulates inside the delta. Although this leads to a slight increase in losses, the circulating current facilitates the exchange of active power between phases, which can be used to balance capacitor voltages especially when negative-sequence reactive power exchange with the grid is needed. This also results in an increased current rating as compared to balance condition (and consequently higher current rating compared to the star). Higher current rating not only affects the rating of the semiconductors in the bridges, but more importantly affects the voltage ripple, and thereby the rating of the capacitors in each bridge. With the same reasoning, the star configuration needs to be over-rated in terms of voltage when operated under unbalanced grids, due to the needed zero-sequence voltage (which will lead to a movement of the floating *Y*-point of the converter) to guarantee capacitor voltage balancing.

Chapter 2. Multilevel converter topologies and modulation techniques overview

Fig. 2.8 Double star configuration with half-bridge cells (known as MMC).

Regarding the double-star configurations, CHB and MMC are "five-terminal circuits" because two neutral points of upper and lower arms are used as the two DC terminals. This is the main advantage of these configurations over star and delta since they can manipulate active power without the need of isolated DC sources in each cell. This is particularly important in High Voltage DC (HVDC) and motor drive applications, where large amount of active power is transfer. However, being the focus of this thesis on STATCOM applications only, a common DC-link between the three phases is not needed.

In STATCOM application the converter must be able to provide reactive power under unbalanced condition. Double star configurations, similar to the delta, have the ability to exchange negative-sequence current with the grid by controlling the circulating current. One of the other important feature of the double-star configuration is the lower device current rating of the individual cells, due to the AC current sharing between the two converter arms. However, the voltage rating of these devices is higher compare with the star and delta. As it is shown in Fig. 2.8 each converter arm generates an AC voltage with a DC offset equal to half of the total DC-link

Fig. 2.9 Double star with CHB configuration.

voltage in MMC. This results in a higher converter arm voltage rating (two times the AC voltage). If H-bridge cells are used instead of half-bridge cells, each arm is needed to generate only the AC voltage with the same amplitude of the output voltage. Therefore the number of cells reduces to half as compare with the double star with half-bridge while the number of power semiconductor in each cell is now doubled. As an example, if half- and H-bridge cells with 1pu voltage rating are available, in order to generate an AC voltage with 1pu peak under balanced conditions, only one cell per phase is needed if star configuration is chosen while  $\sqrt{3}$  cells are needed for delta. Double star configuration with half-bridge cells needs 4 half-bridge cells and double star configuration with H-bridge cells needs 2 H-bridge cells to satisfy the requirements.

The interaction between DC offset voltage at each arm and fundamental current in double star configuration results in a large fundamental frequency component in the arm capacitor voltages. This increases the capacitor voltage ripple as compared with the star and delta configurations. Thus the size of the capacitors and hence cost and footprints increase significantly in the double star configuration.

Double-star configuration with H-bridge cells is superior to the one with half-bridge cells since it has additional buck and boost functions of the DC-link voltage. Having H-bridge cells enables this configuration to tolerate a broad range of variation in the DC-link voltage. This feature makes it suitable for renewable resources such as wind and solar power since the DC-link

### Chapter 2. Multilevel converter topologies and modulation techniques overview

voltage varies with weather variations. Moreover, this configuration has the ability to suppress fault currents arising from DC-side short circuit events [41]. However, this configuration leads to an increased number of semiconductors and specially switching losses as compared with the classical MMC [42].

In STATCOM applications, where only reactive power is exchanged with the grid, star and delta configurations have superior performances. Besides having a less complex controller they have higher efficiency, need less number of cells [43] and have better dynamic performance [28]. Table 2.2 summarizes different characteristics of all modular subset configurations discussed in this chapter.

This section introduces the main modular configurations. Several alternative modular configurations can be found in literature [44,45].

TABLE 2.2. Summery of modular subset configurations characteristics

|                                     | star                    | delta                            | double star             | double star<br>CHB        |

|-------------------------------------|-------------------------|----------------------------------|-------------------------|---------------------------|

| Cell numbers balanced condition     | $v_{ m ac}/V_{ m dc}$   | $\sqrt{3}^{v_{ m ac}}/v_{ m dc}$ | $4^{ m Vac}/V_{ m dc}$  | $2^{v_{ m ac}}/V_{ m dc}$ |

| current rating balanced condition   | $\sqrt{3}$ /phase       | 1/phase                          | 0.5/phase               | 0.5/phase                 |

| Negative-sequence compensation      | capable $(v_0)$         | Capable( $i_0$ )                 | Capable( $i_0$ )        | Capable( $i_0$ )          |

| Circulating current                 | No                      | Yes                              | Yes                     | Yes                       |

| Voltage rating unbalanced condition | Balanced voltage+ $v_0$ | No change                        | No change               | No change                 |

| Current rating unbalanced condition | No change               | Balanced current+ $i_0$          | Balanced current+ $i_0$ | Balanced current+ $i_0$   |

| Capacitor size balanced condition   | Higher than delta       | -                                | Higher than starδ       | Higher than starδ         |

| Capacitor size unbalanced condition | Lower than delta        | -                                | Higher than starδ       | Higher than starδ         |

| Hardware complexity                 | Lowest                  | -                                | -                       | -                         |

| Controller complexity               | Medium                  | Medium                           | High                    | High                      |

| Cost                                |                         | capacitor & s                    | witch trade off         |                           |

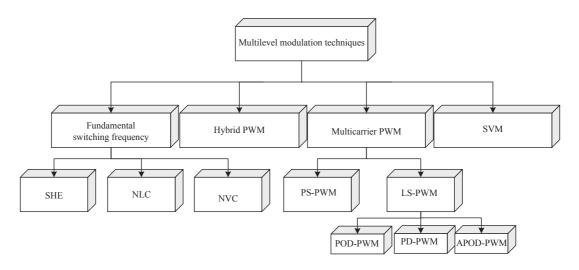

Fig. 2.10 Multilevel converter modulation techniques.

# 2.4 Multilevel converter modulation techniques

The modulator determines the switching function of a converter. In general, the modulation technique must guarantee that the generated voltage at the output of the converter is similar to the desired voltage as much as possible. The challenge is to extend traditional modulation techniques to the multilevel case, where the large number of cells gives different alternatives to modulate the converter. Each modulation approach focuses on the optimization of some converter features such as switching loss reduction, uniform switching loss distribution, improving harmonic performances, common-mode voltage minimization, minimum computational cost, etc. The most common modulation techniques for multilevel converters are summarized in Fig. 2.10.

The fundamental switching modulators provide a switching function such that each cell has only one commutation per fundamental cycle. The switching function with multicarrier PWM are determined based on comparison between the carriers and a modulation index. Hybrid PWM is a mixture of fundamental and carrier-based modulation. Space Vector Modulation (SVM) considers all the possible switching states and selects the best combinations in each control cycle to generate an output voltage with equal volt/second as the reference value. Detail description of each modulator is provided in this section.

It is also worth mentioning that the switching commands for the converter are not always determined by a dedicated modulation stage; instead, they can be determined by a direct consequence of the overall converter controller. Hysteresis current controller and Model Predictive Control (MPC) are typical examples of these type of controllers.

#### 2.4.1 Multicarrier PWM

1. *Phase – Shifted PWM (PS – PWM)*: This method is a natural extension of the traditional bipolar and unipolar PWM techniques. This modulation technique is one of the most commonly used modulation techniques for multilevel converters with half or H-bridge

Chapter 2. Multilevel converter topologies and modulation techniques overview

cells, such as CCC and all the modular configurations.

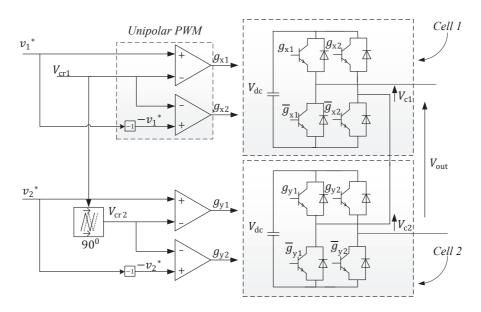

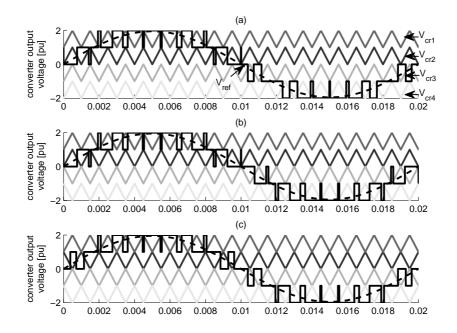

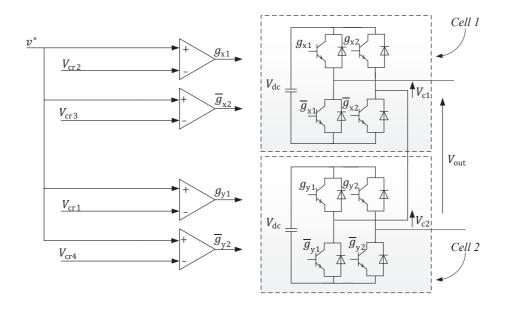

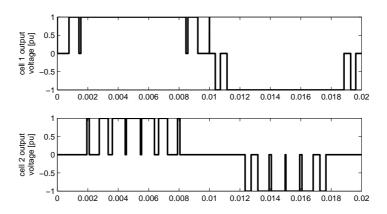

The hardware implementation and operating principle of the PS-PWM for one phase of a five-level star configuration are illustrated in Fig. 2.11 and Fig. 2.12, respectively. Each cell is modulated independently through the comparison between a modulation index and a carrier. The modulation index is the same for all the cells that constitutes a phase leg, while a phase shift is introduced between the carrier signals of each cell within the same phase. It is proven that the lowest distortion at the total output can be achieved when the phase shifts between carriers are  $180^{0}/n$  (where n is the number of cells per phase).

Since the modulation signals and carrier frequency are the same for all the cells, the switching pattern and thereby the active power are evenly distributed among all the cells [31]. The advantage of the even power distribution is that, in case of CHB-STATCOM as an example, once the DC-link capacitors are properly charged, no unbalance will be produced among the DC-link voltages, at least under ideal conditions. Moreover, due to the proper selection of the phase shift angle between carriers, the total output waveform has a switching pattern with n times the switching pattern of each cell. Hence, better Total Harmonic Distortion (THD) is obtained at the output, using n times lower carrier frequency.

Fig. 2.11 Hardware implementation of PS-PWM for one phase of a five-level star based on unipolar PWM.

Fig. 2.12 Operating principle and switching pattern of the PS-PWM based on unipolar PWM.

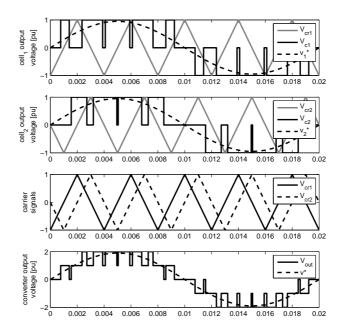

2. Level – Shifted PWM (LS – PWM): This method is a natural extension of traditional bipolar PWM techniques. In traditional bipolar PWM, a carrier signal is compared with the reference to decide between two different voltage levels. If the reference voltage is greater than the carrier then a switching command that generates the positive voltage level is sent to the converter. In another case, if the reference is less than the carrier, a switching command that generates the negative voltage level is sent.

By extending this idea for a multilevel converter with *m* levels, *m* – 1 carriers are needed. Each carrier is set between two voltage levels and the same principle of bipolar PWM is applied. Required carriers can be arranged in vertical shifts. If all the carriers are in phase with each other (only vertical shift), the modulation technique is named Phase Disposition PWM (PD-PWM). If all the positive carriers are in phase with each other and in opposite phase with the negative carriers, we talk about Phase Opposition Disposition PWM (POD-PWM). By alternating the phase between adjacent carriers, Alternate Phase Opposition Disposition PWM (APOD-PWM) is obtained. Different arrangement of carriers provides different THD. For example POD-PWM at the expense of having more complicated structure than PD-PWM has less THD than the later [46],[47]. An example of these arrangements for a five-level (thus four carriers) star configuration is given in Fig. 2.13. The switching command must be wisely directed to the appropriate power semi-conductors in order to generate the corresponding levels. The hardware implementation and cell output voltage by using LS-PWM for a five-level star configuration is illustrated in Fig. 2.14.

This modulation technique can be adapted to any multilevel converter. However, as it can be observed from Fig. 2.15, it is clear that the switching pattern is not uniform between

Fig. 2.13 LS-PWM arrangement; (a): PD; (b): POD; (c): APOD.

Fig. 2.14 Hardware implementation of LS-PWM.

Fig. 2.15 Cell output voltages by using LS-PWM.

two cells when LS-PWM is used. This causes an uneven power distribution among the different cells.

## 2.4.2 Space Vector Modulation (SVM)

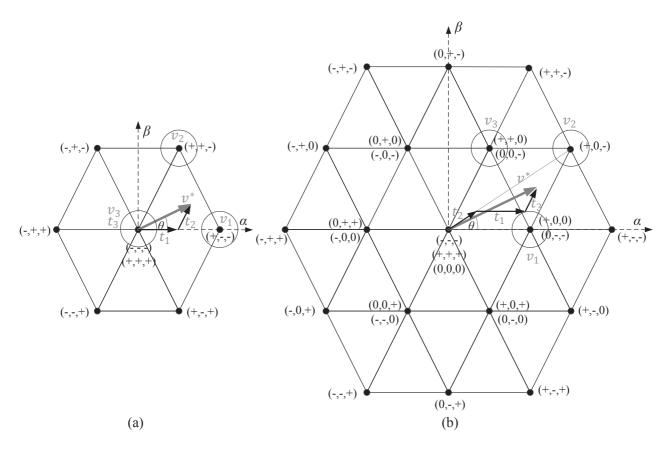

Using Fig. 2.16 (a), the different steps of SVM can be summarized as follows. First step is to determine all the switching states and their corresponding state-space vector in the  $\alpha\beta$ -reference frame. Fig. 2.16 (a) shows all the eight switching space vectors with black circles for a traditional two level converter. + and - signs in parentheses are to show which switch in each phase is on. For example (-,+,+) shows that in phase a lower switch and in the other two phases upper switches are on.

Second step is to determine the reference voltage state-space vector in  $\alpha\beta$ -reference frame. Third step is to find the three closest switching combination to the reference  $(v_1, v_2, v_3)$  in Fig. 2.16 (a)). The final step is to calculate the time duration of each switching state  $(t_1, t_2)$  so that the time average of the generated voltage equals the reference space vector.

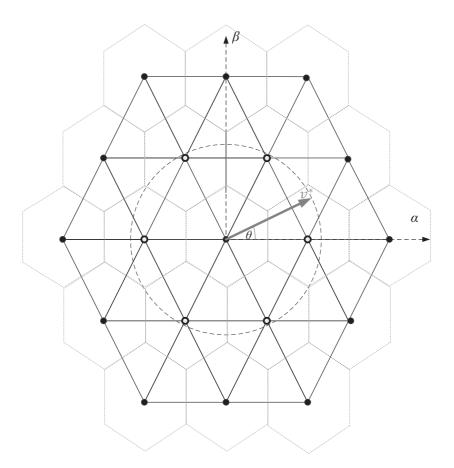

Figure 2.16 (b) shows the extension of SVM for a three level star configuration (one cell per phase). Each cell can produce positive ( $+V_{\rm dc}$ ), negative ( $-V_{\rm dc}$ ) and zero (0) voltage levels. Having 3 levels, results in  $3^3$  possible combinations, shown with black circles. It can be observed that for some vectors more than one switching state is possible.

Following the same steps as explained before  $v_1, v_2, v_3$  and their corresponding time  $t_1, t_2, t_3$  should be determined in order to provide the switching commands.

It should be noted that SVM explained here is valid only for a balanced system with purely sinusoidal reference voltages. In case of an unbalanced system, existence of harmonics or zero-sequence component this algorithm must be modified [48, 49].

Fig. 2.16 SVM principle for; (a): traditional two level converter; (b): three-phase three-level star configuration.

## 2.4.3 Fundamental switching modulators

1. Selective Harmonic Elimination (SHE): The basic idea behind SHE is predefining and precalculating the switching angles per quarter-fundamental cycle via Fourier analysis, to ensure the elimination of undesired low-order harmonics. The first step is to find the Fourier series of the multilevel waveform based on unknown switching angles. Next step is to set the undesired Fourier coefficient to zero, while the fundamental component is made equal to the desired reference value. The obtained equations are solved offline using numerical methods, finding the proper solution for the angles.

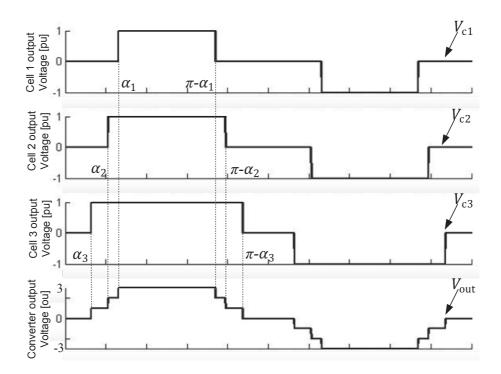

As an example for phase a of the star configuration with three H-bridges per phase, a typical waveform considering three switching angles  $(\alpha_1, \alpha_2, \alpha_3)$  is given in Fig. 2.17. Each angle is associated to a particular cell. Consequently, each cell of the converter produces positive or negative voltage levels at a specific angle only once in a fundamental cycle. SHE is also known as staircase modulation because of the stair-like shape of the voltage waveform.

Note that there is no control over non-eliminated harmonics and if non-eliminated harmonic amplitude are not suitable for a particular application, additional cells and angles should be introduced. It is also possible to limit the harmonic content to acceptable val-

Fig. 2.17 SHE technique for phase a of the star configuration with 3 cells per phase.

ues instead of completely eliminating them. This method is called Selective Harmonic Mitigation (SHM).

The main advantage of SHE is the reduction of the switching frequency and consequently of the switching losses. It also eliminates the low order harmonics, facilitating the reduction of output filter size. However, this method requires numerical algorithms to solve the equations for different modulation indexes. With current technology of microprocessors it is not possible to do the calculations in real time. Therefore, the solutions are stored in a look-up table, and interpolation is used for those unsolved modulation indexes. This makes SHE method not suitable for applications where high dynamic performance is needed.

2. Nearest Vector Control (NVC): NVC also known as State Vector Control is the alternative method to SHE to provide a low switching frequency, without the disadvantages of numerical calculation and poor dynamic performance. The basic idea is to simply approximating the reference voltage to the closest voltage vectors that can be generated in the  $\alpha\beta$  frame.

The dots in Fig. 2.18 shows all the possible voltage vectors generated by the converter, surrounded by the hexagons. Each converter vector is considered as the closest vector to the reference, as long as the reference voltage is located inside the hexagon surrounded that vector. Hence, when the reference voltage falls into a certain hexagon, the corresponding vector is generated by the converter.

Unlike SHE, this technique does not eliminate low-order harmonics. However, this problem can be avoided by using multilevel converters with a high number of levels. High

Chapter 2. Multilevel converter topologies and modulation techniques overview

Fig. 2.18 All the possible voltage vector for a three-level star configuration and their corresponding hexagon.

number of levels provides more available voltage vectors and thereby smaller error. Despite the simple operating principle, its practical implementation is not trivial.

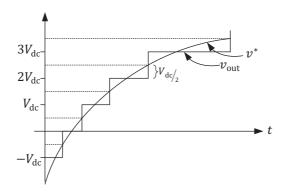

3. Nearest level Control (NLC): NLC, also known as round method, is somehow the perphase time domain counterpart of the NVC. The basic principle in both methods is the same, but instead of choosing the closest vector, when using NLC the voltage level closest to the reference voltage is selected. Also unlike NVC, where three phases are controlled simultaneously with the vector selection, here three phases are controlled independently with 120<sup>0</sup> phase shifted references. The main advantage of this method over NVC is that since finding the closest level is much easier than finding the closest vector to the reference, NLC is greatly simplified in relation to NVC.

The output voltage using NLC is shown in Fig. 2.19 for the first quarter cycle of the reference voltage, where  $V_{\rm dc}$  is the voltage difference between two voltage levels (usually the DC-link voltage in modular configurations),  $v^*$  is the reference voltage and  $v_{\rm out}$  is the output voltage. As can be seen from Fig. 2.19 the maximum error in approximation of the closest voltage level is  $V_{\rm dc}/2$ .

Similar to NVC, NLC does not eliminate specific low-order harmonics. Therefore, both

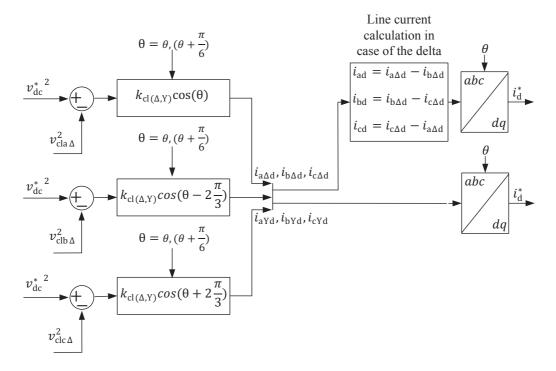

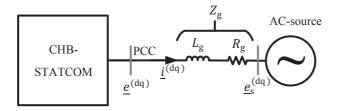

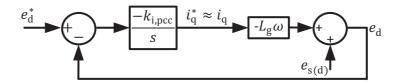

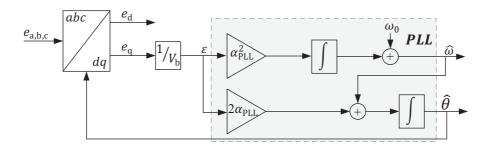

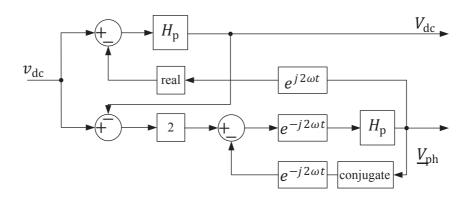

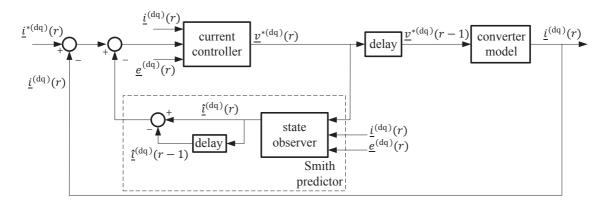

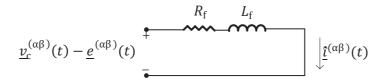

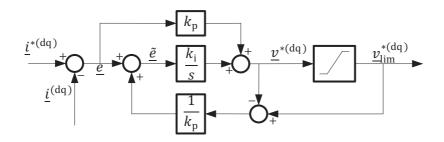

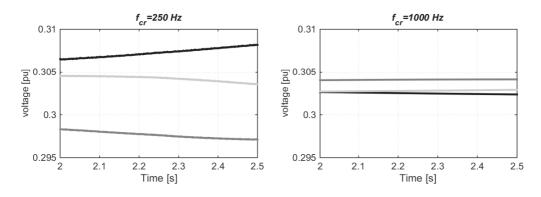

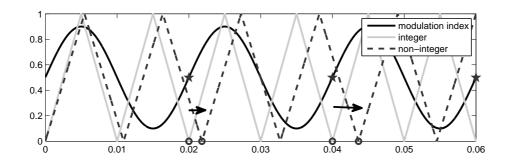

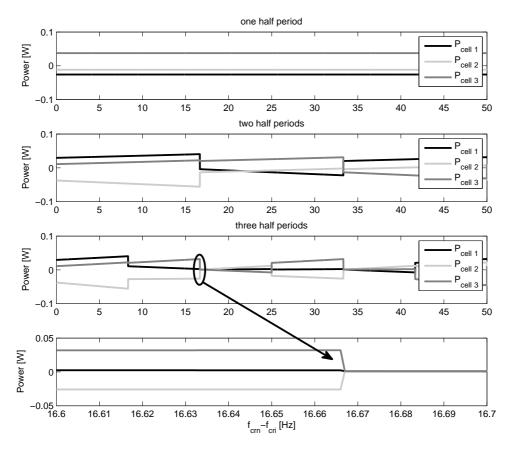

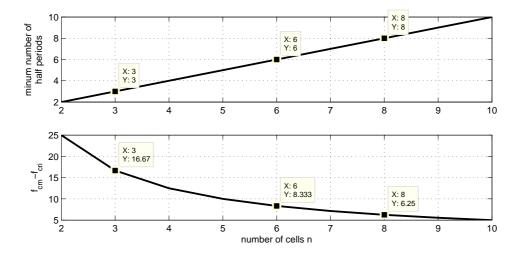

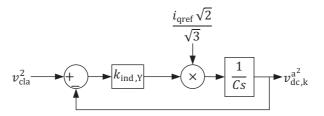

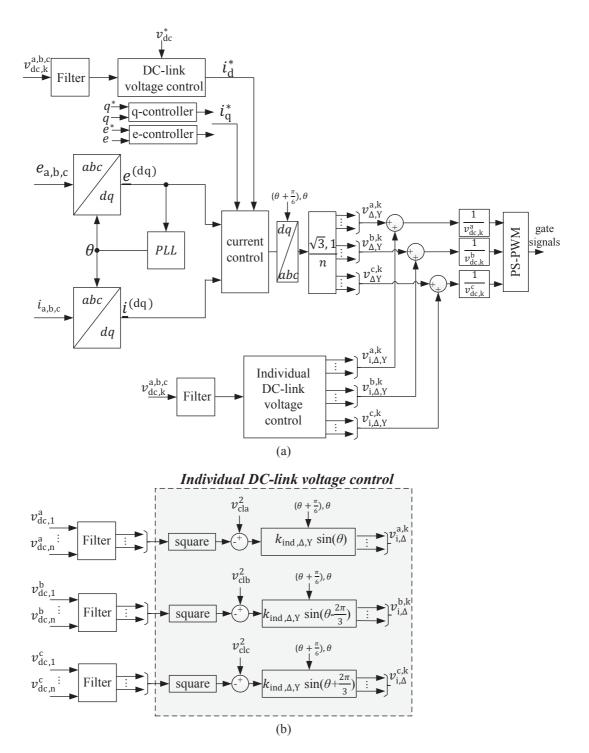

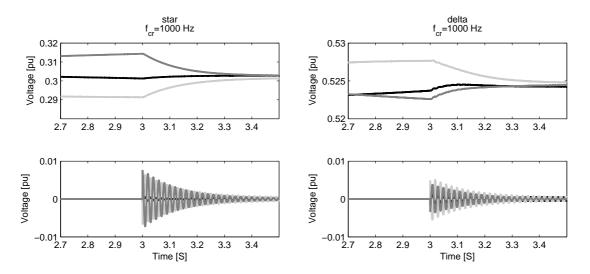

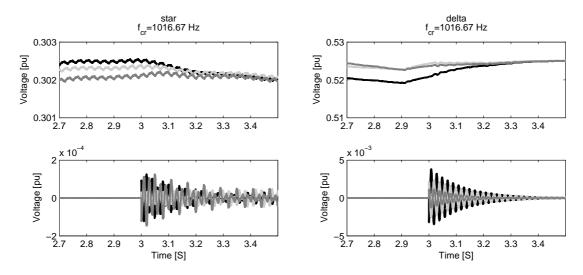

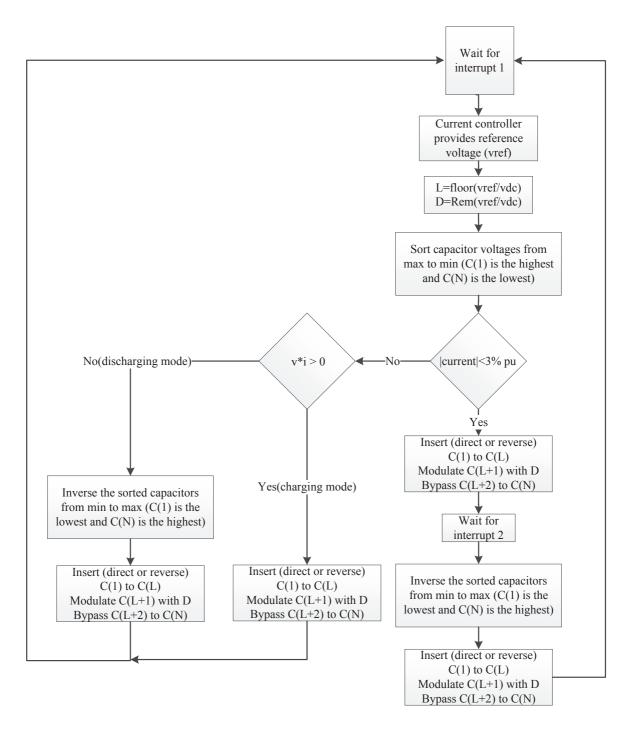

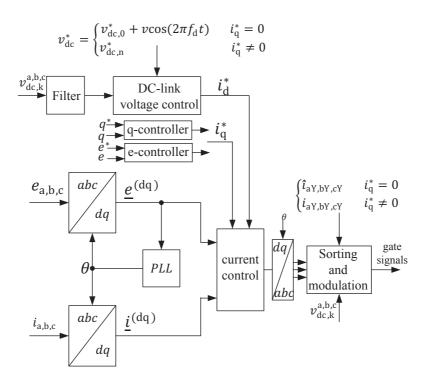

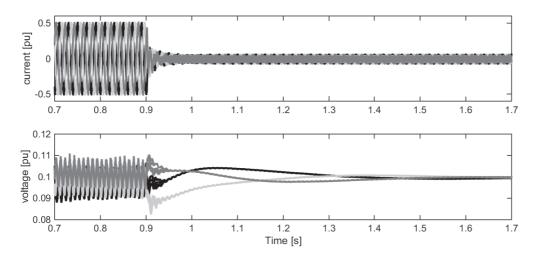

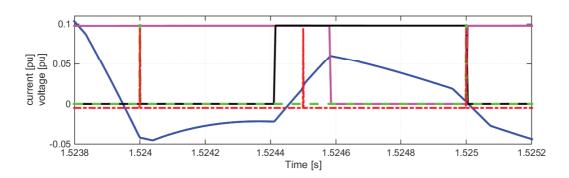

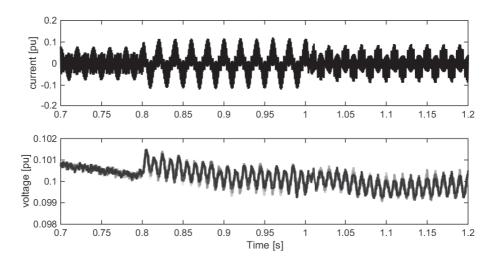

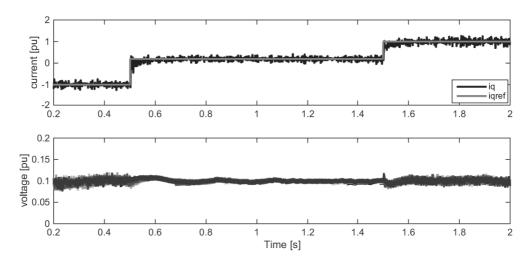

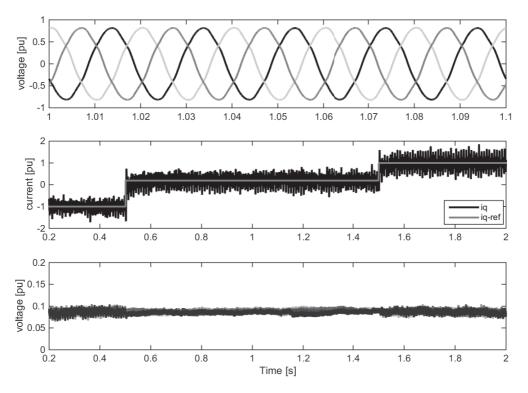

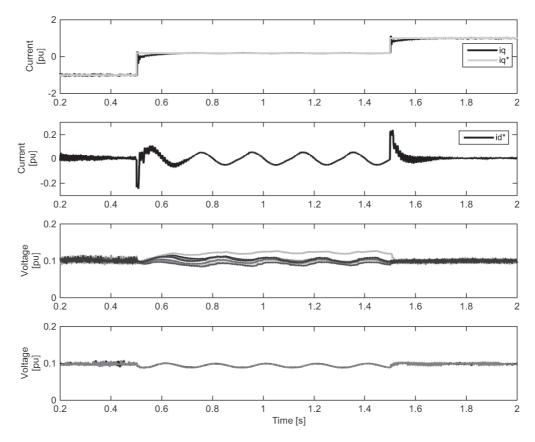

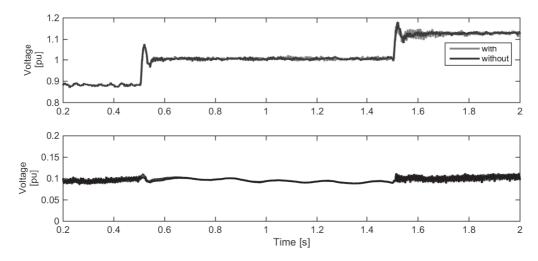

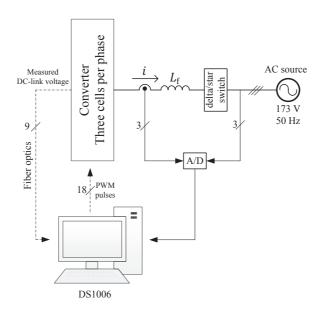

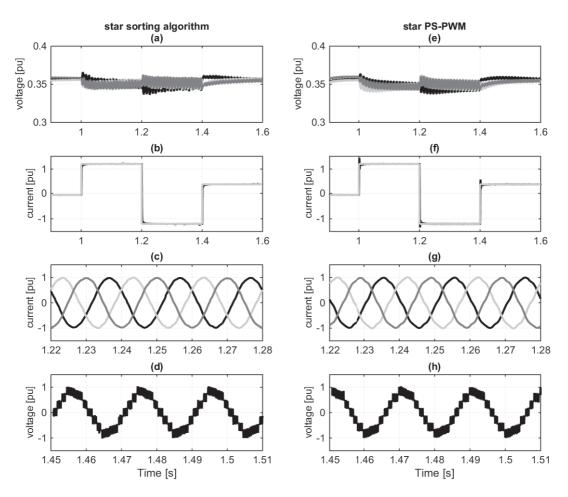

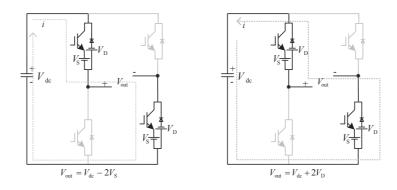

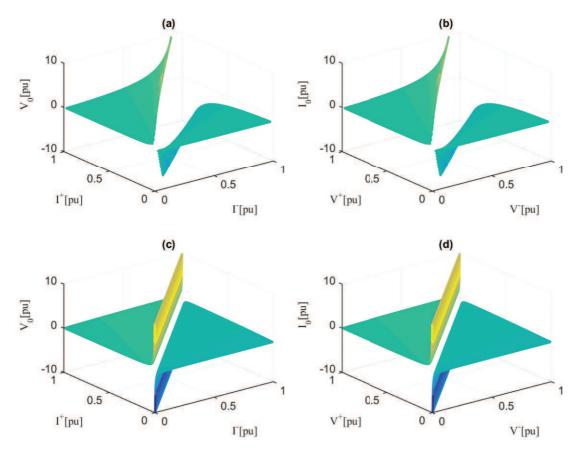

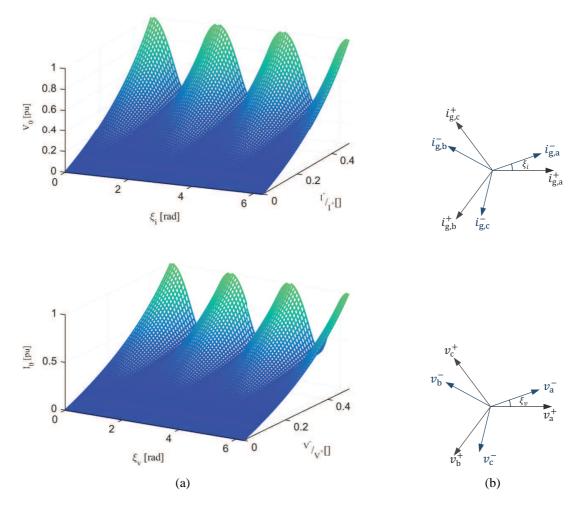

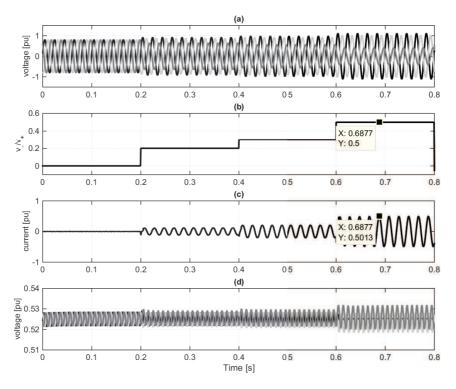

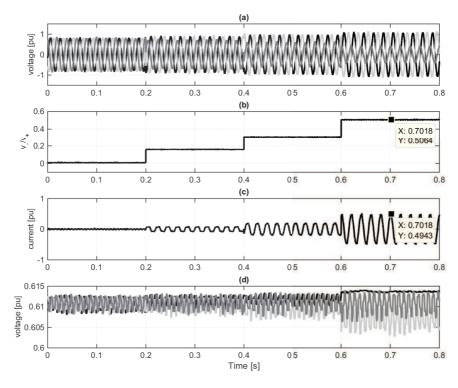

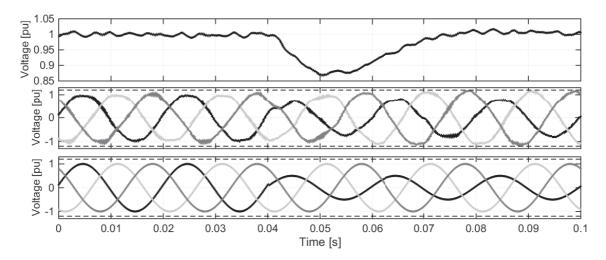

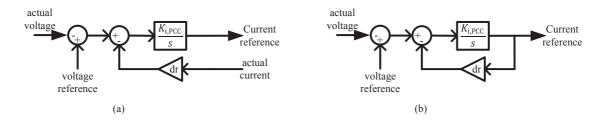

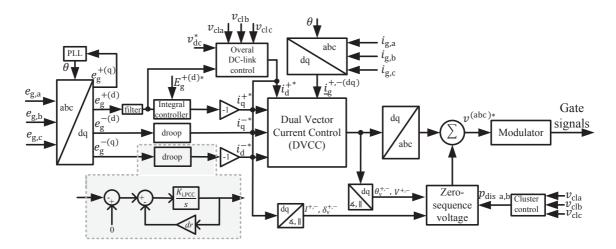

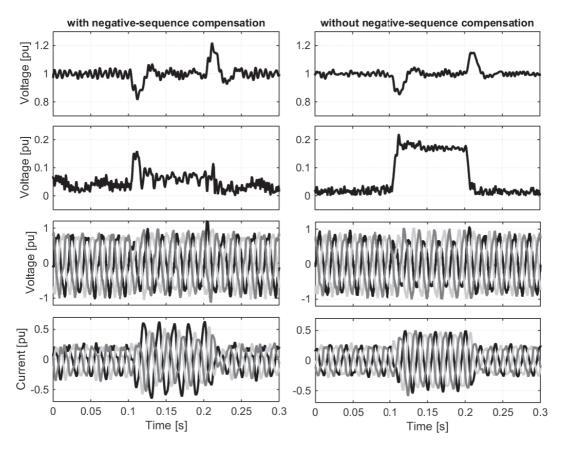

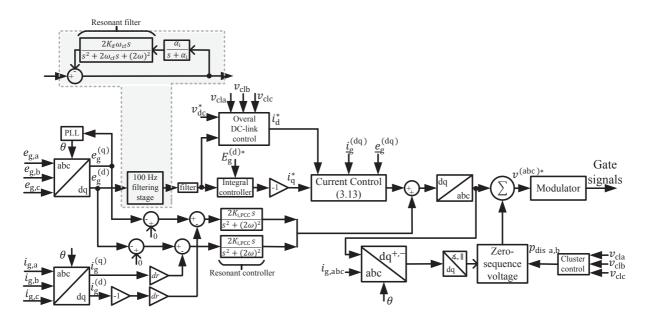

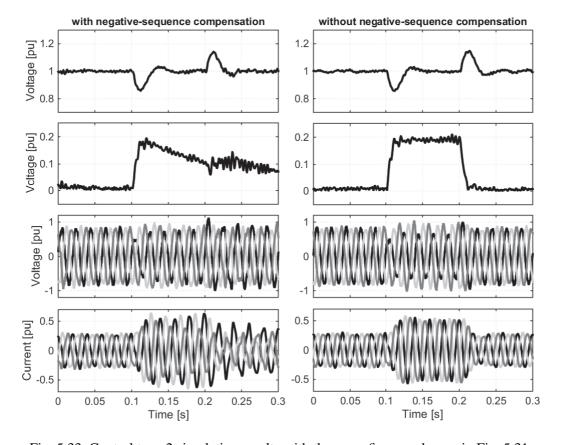

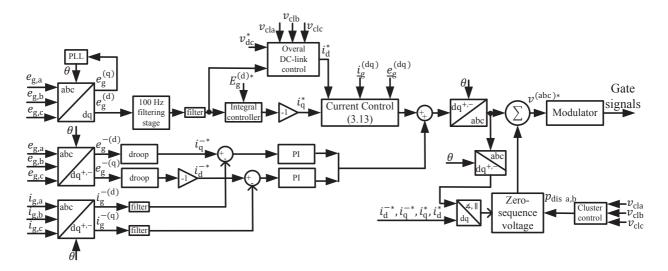

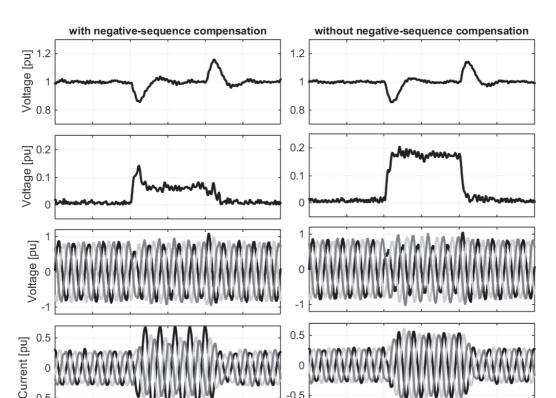

Fig. 2.19 The output voltage waveform using NLC.